# MNM1221

# **100 Mbps Communication ASIC**

# For RTEX

# Datasheet

Motion Control Business Unit

Industrial Device Business Division

Panasonic Industry Co., Ltd.

# **Revision History**

| Revision | Date      | Change Description |                                                               |  |  |

|----------|-----------|--------------------|---------------------------------------------------------------|--|--|

| 0.1      | 2004/5/6  | Initial Relea      | Initial Release (Preliminary)                                 |  |  |

| 1        | 2011/9/13 | P1                 | Changed title and company name.                               |  |  |

|          |           | P8                 | Updated introduction and features.                            |  |  |

|          |           | P10                | Updated recommended PHY.                                      |  |  |

|          |           | P15                | Clarified timing between XSYNC and transmitting.              |  |  |

|          |           | P16                | Clarified that JTAG pins cannot be used in normal operation.  |  |  |

|          |           | P25                | Updated communication period description.                     |  |  |

|          |           | P27                | Clarified description for RX bank switching.                  |  |  |

|          |           | P39                | Corrected period setting value.                               |  |  |

|          |           | P46                | Renamed "recovering function" to "error correcting function". |  |  |

|          |           | P51-56             | Added MII register access section.                            |  |  |

|          |           | P57-94             | Added slave operation chapter.                                |  |  |

|          |           |                    | Renamed "Servo slave" to "Generic slave".                     |  |  |

|          |           | P97                | Added maximum current consumption.                            |  |  |

|          |           | P102               | Added ordering information.                                   |  |  |

| 2        | 2012/2/22 | P16                | Added pin16 as ADDVDD and pin61 as ADDVSS.                    |  |  |

| 3        | 2024/5/9  | P10                | Updated the recommended PHY and magnetics.                    |  |  |

|          |           | P16                | Added 5T as XRST type.                                        |  |  |

|          |           | P24-25             | Added "Frame Structure".                                      |  |  |

|          |           | P26-29             | Added "Frame Descriptions".                                   |  |  |

|          |           | P30                | Modified "Time Chart at Start-up".                            |  |  |

|          |           | P31                | Updated the communication period.                             |  |  |

|          |           | P38                | Added the descriptions on "Chip Reset".                       |  |  |

|          |           | P45                | Updated the setting example on "Transmission Period".         |  |  |

|          |           | P48                | Modified Frame ID description on "Communication State".       |  |  |

|          |           | P50-53             | Clarified the descriptions on "Error Flags 1, 2".             |  |  |

|          |           | P69-71             | Corrected the condition of the state change for RUNNING.      |  |  |

|          |           | P78                | Added the descriptions on "Chip Reset".                       |  |  |

|          |           | P88                | Modified Frame ID description on "Communication State".       |  |  |

|          |           | P90-91             | Clarified the descriptions on "Error Flags".                  |  |  |

|          |           | P108-109           | Added the description for XWAIT.                              |  |  |

# **Table of Contents**

| CHAPTER 1 GENERAL DESCRIPTION         | 7  |

|---------------------------------------|----|

| OVERVIEW                              |    |

| Introduction                          | 8  |

| Features                              |    |

| Applications                          |    |

| System Diagram                        |    |

| Detail of a Node                      |    |

| Block Diagram of MNM1221              |    |

| PIN DESCRIPTIONS                      |    |

| Pin Assignments                       |    |

| Master Pin Descriptions               |    |

| Slave Pin Descriptions                |    |

| Operating Mode Settings               |    |

| CONNECTION TO PHY WITH MII            |    |

| CHAPTER 2 MASTER OPERATION            | 20 |

| CONNECTION FOR MASTER OPERATION       |    |

| Mode Setting                          |    |

| Bus interface between MNM1221 and CPU |    |

| FUNCTIONAL DESCRIPTION                |    |

| State Transition of MNM1221           |    |

| Descriptions of Each State            |    |

| Frame Structure                       |    |

| Frame Descriptions                    |    |

| Time Chart at Start-up                |    |

| Transmission in RUNNING State         |    |

| TX and RX Memory in MNM1221           |    |

| Assignment on TX and RX Memory        |    |

| MEMORY MAP                            |    |

| REGISTERS DESCRIPTION                 |    |

| Table of Registers                    |    |

| Chip Reset                            |    |

| Initial Frame Transmit                |    |

| Cyclic Transmission Start             |    |

| Real-Time Frame Format                  | 41 |

|-----------------------------------------|----|

| Error Counter Setting                   | 42 |

| Initializing Done                       | 43 |

| Transmit Timing Select                  |    |

| Transmission Period                     | 45 |

| Transmission Memory Switch              |    |

| Receiving Memory Hold                   | 47 |

| Communication State                     | 48 |

| Initializing Error                      | 49 |

| Error Flags 1 (Errors at RING CONFIG)   | 50 |

| Error Flags 2 (Errors at RUNNING)       | 52 |

| Data CRC Errors                         | 54 |

| Slave Node Sum                          | 55 |

| Data Block Sum                          | 56 |

| Slave Information                       | 57 |

| MII REGISTER ACCESS                     | 59 |

| Table of Registers                      | 59 |

| MDIO Write Data                         | 60 |

| MDIO Address                            | 61 |

| MDIO Write Command                      | 62 |

| MDIO Read Command                       | 63 |

| MDIO Read Data                          |    |

| CHAPTER 3 SLAVE OPERATION               | 65 |

| OVERVIEW                                |    |

| Introduction                            |    |

| Features in Slave                       |    |

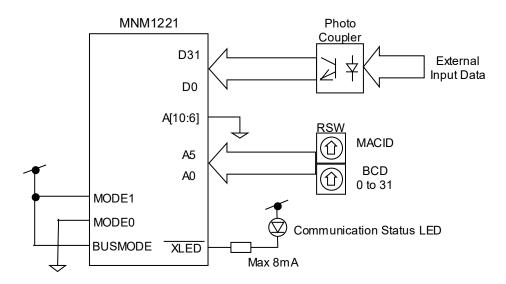

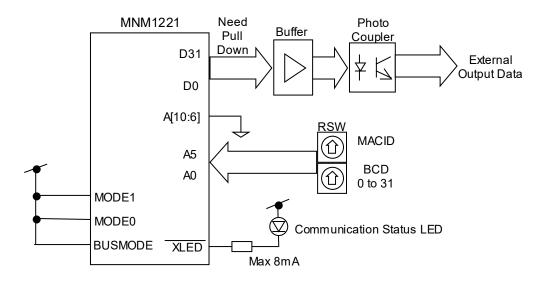

| CONNECTION FOR SLAVE                    | 67 |

| Bus Interface with CPU in Generic slave | 67 |

| Connection for IN slave                 |    |

| Connection for OUT slave                | 68 |

| FUNCTIONAL DESCRIPTION                  | 69 |

| State Transition of MNM1221             | 69 |

| Descriptions of Each State              |    |

| Time Chart at Start-up                  |    |

| Timing Signal Output                    |    |

| Transmission in RUNNING state          | 73        |

|----------------------------------------|-----------|

| TX and RX Memory in MNM1221            | 74        |

| Location in TX and RX Memory           | 75        |

| MEMORY MAP                             | 76        |

| REGISTERS DESCRIPTION                  | 77        |

| Table of Registers                     | 77        |

| Chip Reset                             | 78        |

| MAC-ID Setting                         | 79        |

| Number of Occupied Blocks              | 80        |

| Timeout Setting                        | 81        |

| Initializing Done                      | 82        |

| INTRX Mask at Timeout                  | 83        |

| SYNC Output Delay                      | 84        |

| SYNC Output Mask                       | 85        |

| Transmission Memory Switch             | 86        |

| Receiving Memory Hold                  | 87        |

| Communication State                    | 88        |

| Over Number of Slave                   | 89        |

| Error Flags                            | 90        |

| Data CRC Errors (L)                    | <i>92</i> |

| Data CRC Errors (H)                    | 93        |

| My Node Order                          | 94        |

| My Block Order                         | 95        |

| Slave Node Sum                         | 96        |

| Data Block Sum                         | 97        |

| MII REGISTER ACCESS                    | 98        |

| Table of Registers                     | 98        |

| MDIO Write Data                        | 99        |

| MDIO Address                           | 100       |

| MDIO Write Command                     | 101       |

| MDIO Read Command                      | 102       |

| MDIO Read Data                         | 103       |

| CHAPTER 4 COMMON TO MASTER AND SLAVE 1 | .04       |

| ELECTRICAL CHARACTERISTICS             | _05       |

| Absolute Maximum Ratings               | 105       |

| Recommended Operating Conditions |  |

|----------------------------------|--|

| DC Characteristics               |  |

| AC Characteristics               |  |

| DIMENSIONS                       |  |

| SOLDERING INFORMATION            |  |

| ORDERING INFORMATION             |  |

# Chapter 1 General Description

# Overview

#### Introduction

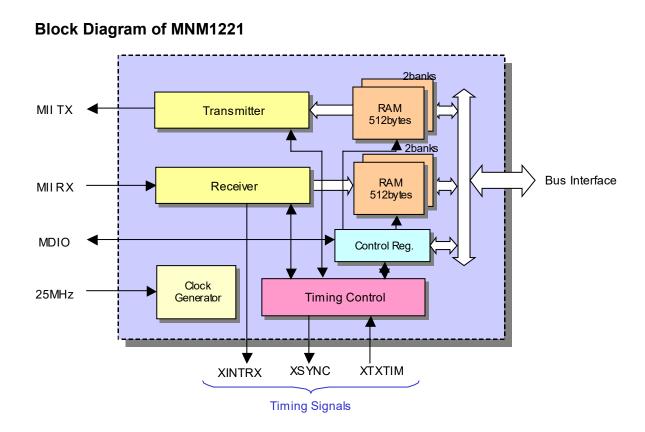

MNM1221 is a serial interface controller ASIC that enables to establish the real-time communication systems "*Realtime Express (RTEX)*" based upon the master-slaves communication style with the ring topology. The MNM1221 requires to be used with a PHY (PHYsical layer chip), a pulse transformer and shielded twisted pair cables for 100BASE-TX (IEEE 802.3u) system. In other words, MNM1221 is a special MAC(Media Access Controller) in order to suit 100BASE-TX to real-time communication system for the multi-axis servo control.

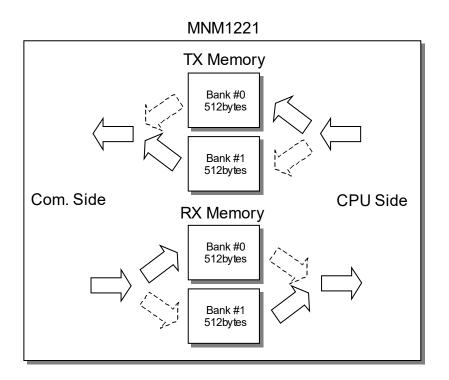

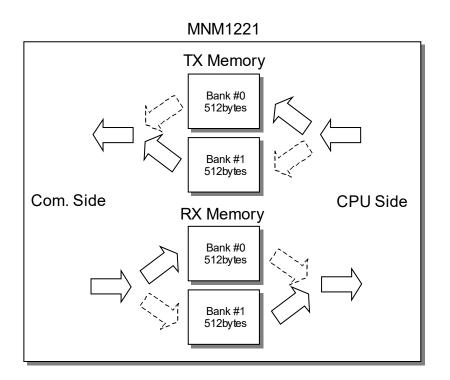

The MNM1221 serial interface system consists of one master and several slaves, and exchanges the command data from the master and the response data from the slave cyclically. For that, MNM1221 has double banks (buffer) memory for each transmitting and receiving, and this function allows the CPU to operate efficiently.

# Features

- Connected to the PHY with MII (Media Independent Interface) by IEEE 802.3u

- Ring topology

- 100 Mbps Full-Duplex

- For both master and slave mode operation

- Maximum 32 slaves

- Double banks (buffer) memory, size of 512 bytes each for RX and TX.

- Data bus for CPU interface:

- Master: 32-bit or 16-bit wide

Slave: 16-bit or 8-bit wide

- Data error detection based on CRC-CCITT(16bits CRC)

- 25MHz clock same as driving PHY

- 3.3V operation and partly with 5 V tolerant pins for CPU interface

- -40 to +85 deg C operating ambient

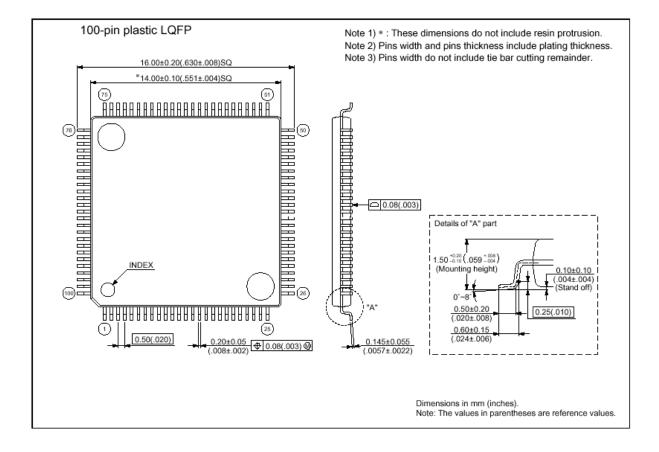

- 100 pins plastic LQFP package of Pb-Free

# Applications

- High performance multi-axis servo control systems

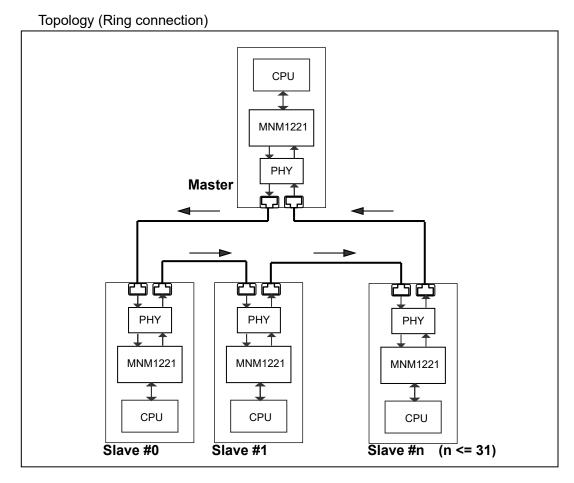

# System Diagram

Notes:

- A hub, required in normal 100BASE-TX system, is not used because of Ring topology.

- Pulse transformers are omitted in the figure.

- STP(Shielded Twisted Pair cable) conforming to CAT5e(category 5 enhanced) or upper should be used.

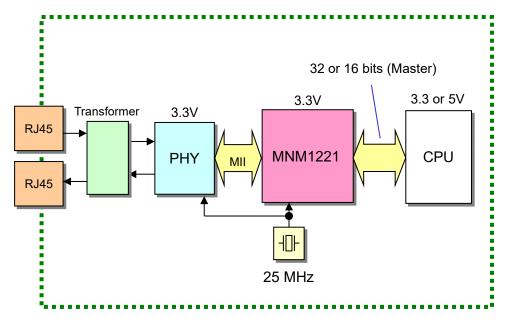

# Detail of a Node

#### Notes about PHY chip:

The pin configuration for the operation must be set as follows. Some PHYs such as DP83822 by TI need MII register setting as well.

- Fixed Full-Duplex

- Disable Auto-Negotiation

- Force 100BASE-TX mode

- Disable Auto-MDIX

| Recommended | PHY: |

|-------------|------|

|             |      |

| Manufacturer | Part Number  | Package     | Ambient Temp.    |

|--------------|--------------|-------------|------------------|

| Broadcom     | BCM5221KPTG  | QFP 64 pins | -40 to +85 deg C |

| ТІ           | DP83848IVV   | QFP 48 pins | -40 to +85 deg C |

| ТІ           | DP83822IRHBR | QFN 32 pins | -40 to +85 deg C |

The pulse transformer (magnetics) suited to each PHY must be selected.

The following is an example. RJ45 connector with built-in magnetics cannot be used.

| Manufacturer | Part Number | Ambient Temp.    |  |

|--------------|-------------|------------------|--|

| Bothhand     | TS8121CM HF | -40 to +85 deg C |  |

| Bothhand     | TS21C HF    | 0 to +70 deg C   |  |

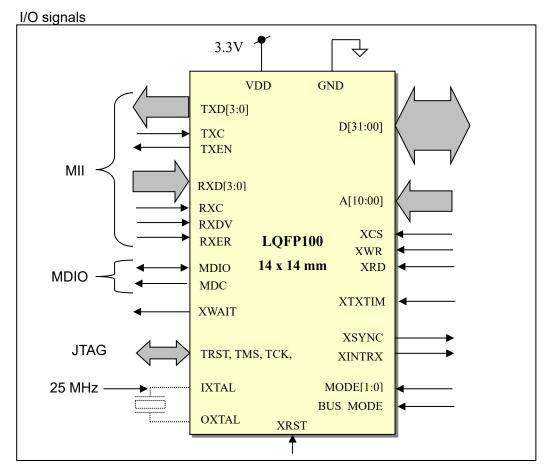

# **Pin Descriptions**

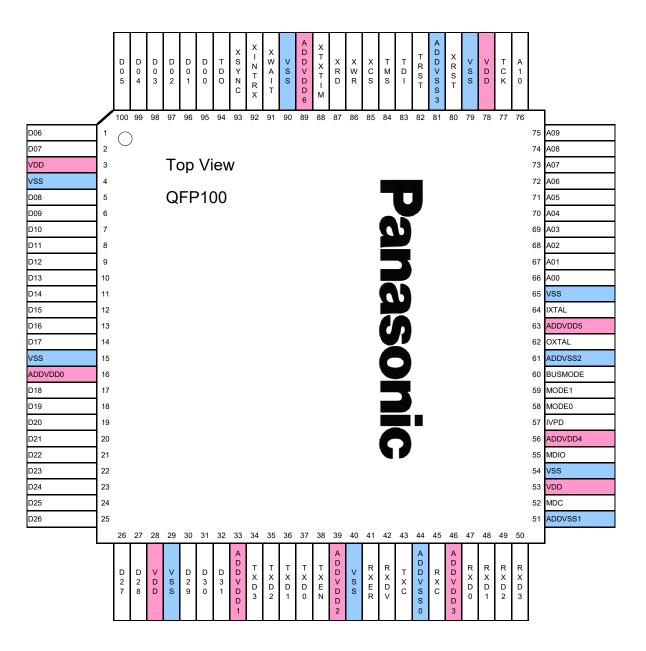

# Pin Assignments

Note:

Ceramic capacitors of about 0.1 uF should be put close to each pair of VDD and VSS.

# **Master Pin Descriptions**

#### Name:

| Prefix | Description           |  |

|--------|-----------------------|--|

| "X"    | Negative Logic        |  |

| Non    | Positive or Non Logic |  |

| Type. |

|-------|

|-------|

| Symbol          | Description                            |  |  |

|-----------------|----------------------------------------|--|--|

| I               | Input                                  |  |  |

| 0               | Output                                 |  |  |

| I/O             | Input/Output                           |  |  |

| I <sub>PD</sub> | Input with internal Pull-Down register |  |  |

| I <sub>PU</sub> | Input with internal Pull-UP register   |  |  |

| 5T 5 V Tolerant |                                        |  |  |

#### Mode:

| Name            | Pin#     | Туре                                     |                                                                                                                                                                         | [                   | Description |         |

|-----------------|----------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|---------|

| MODE1,<br>MODE0 | 59<br>58 | I <sub>PD</sub><br>I <sub>PD</sub><br>5T | Mode Selection:<br>The operating mode is defined by MODE[1:0].<br>Connect both MODE1 and 0 to GND directly.                                                             |                     |             |         |

|                 |          |                                          | MODE 1 MODE 0 Operating mode selected                                                                                                                                   |                     |             |         |

|                 |          |                                          | Low                                                                                                                                                                     | Low                 | Ма          | aster   |

|                 |          |                                          | Low<br>High<br>High                                                                                                                                                     | High<br>Low<br>High | Do not set  |         |

| BUSMODE         | 60       | I <sub>PD</sub><br>5T                    | Bus Mode Selection:The bus size for CPU interface is defined by BUSMODE.Connect to either GND or VDD(3.3 V) directly.In Master mode:BUSMODEDataAddressLowD[15:0]A[10:1] |                     |             |         |

|                 |          |                                          | Hig                                                                                                                                                                     | n                   | D[31:0]     | A[10:2] |

#### MII:

| Name     | Pin#  | Туре | Description                                                                                                                                                                                                                   | At Reset |

|----------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| TXC      | 43    | I    | MII Transmit Clock:<br>TXC is the transmit clock from PHY.<br>The frequency is 25 MHz.<br>A dumping register that is about 33 Ohm should be<br>put near the output pin of the PHY.                                            |          |

| TXD[3:0] | 34-37 | 0    | MII Transmit Data Output:<br>TXD[3:0] are the transmit data synchronized with<br>TXC.                                                                                                                                         | L        |

| TXEN     | 38    | 0    | <b>MII Transmit Enable:</b><br>Indicates that the data on TXD[3:0] is valid.                                                                                                                                                  | L        |

| RXC      | 45    | I    | MII Receive Clock:<br>RXC is the receiving clock from PHY.<br>The frequency is 25 MHz<br>A dumping register that is about 330hm should be<br>put near the output pin of the PHY.                                              |          |

| RXD[3:0] | 47-50 | I    | MII Receive Data Input:<br>RXD[3:0] are the receiving data synchronized with<br>RXC.                                                                                                                                          |          |

| RXDV     | 42    | I    | MII Receive Data Valid:<br>Indicates that the data presented on RXD3-0 is valid.                                                                                                                                              |          |

| RXER     | 41    | I    | MII Receive Error Detected:<br>Indicates that an error is occurring during a receiving<br>frame.                                                                                                                              |          |

| MDIO     | 55    | I/O  | Management Data I/O:<br>This serial input/output is used to read from and write<br>to the MII registers in the PHY. MDIO is<br>synchronized with MDC.<br>An external pull-up register that is about 1.5 k Ohm<br>must be put. | HiZ      |

| MDC      | 52    | 0    | Management Data Clock:<br>MDC is the clock output for serial interface of MDIO.<br>The frequency is 781.25 kHz.                                                                                                               | L        |

#### **CPU interface:**

| Name    | Pin#                                        | Туре      | Description                                                                                                                                                                                                                                                                            | At Reset |

|---------|---------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| D[31:0] | 1,2,<br>5-14,<br>17-27,<br>30-32,<br>95-100 | I/O<br>5T | <b>Data Bus:</b><br>Either 16bits-width via D[15:0] or 32 bits-width via D[31:0] can be used. The 32 bits-width is more recommended for the faster access.<br>In 16 bits case, unused D[31:16] should be pull-downed with external registers that are about 10 k Ohm.                  | HiZ      |

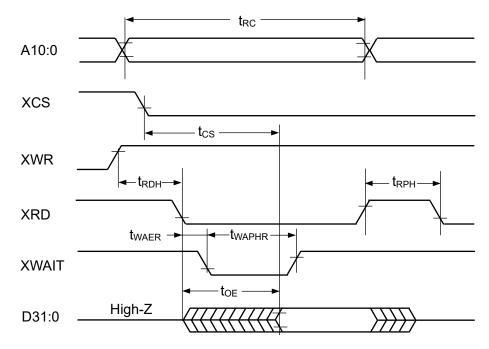

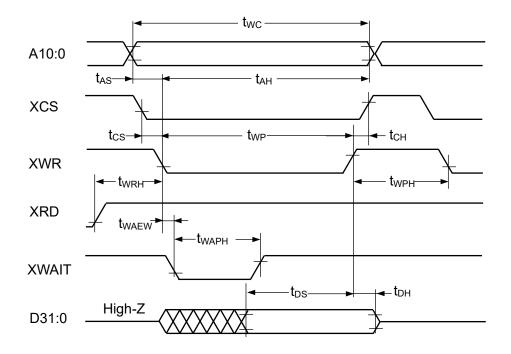

| A[10:0] | 66-76                                       | I<br>5T   | Address Bus:<br>The address data is 11bits-wide via A10-0.<br>But A0 is not used in 16bits data bus, additionally A1<br>is not used in 32 bits data bus. Therefore, the<br>followings are recommended:<br>16 bit bus: Connect A0 to GND.<br>32 bit bus: Connect both A0 and A1 to GND. |          |

| XCS     | 85                                          | l<br>5T   | Chip Select:<br>For this chip selection. Low active.                                                                                                                                                                                                                                   |          |

| XRD     | 87                                          | l<br>5T   | Read (Output) Enable:<br>For read access. Low active.                                                                                                                                                                                                                                  |          |

| XWR     | 86                                          | l<br>5T   | Write Enable:<br>For write access. Low active.                                                                                                                                                                                                                                         |          |

| XWAIT   | 91                                          | 0         | Wait Request:<br>XWAIT indicates the waiting requirement during an<br>access. To ensure the access, XWAIT should be<br>connected to the wait input pin of the CPU.<br>Low active.                                                                                                      | Η        |

# Timing signals:

| Name   | Pin# | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                  | At Reset |

|--------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

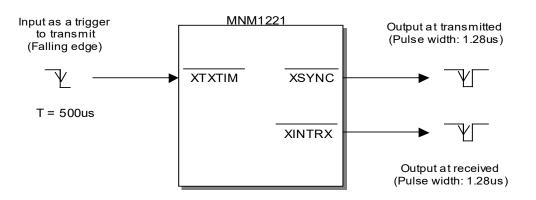

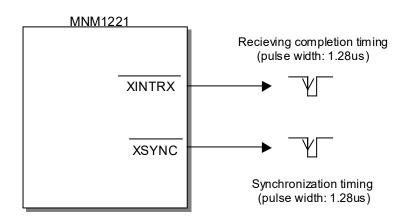

| XSYNC  | 93   | 0       | <b>Transmitted Timing Pulse:</b><br>XSYNC is outputted when starting transmitting the frame. At this pulse output, the transmitting has already started.<br>The falling edge is effective.<br>The pulse width is 1.28 us.                                                                                                                                                                                                    | Η        |

| XINTRX | 92   | 0       | <b>Receiving Interrupt Pulse:</b><br>XINTRX is outputted when completing receiving the frame.<br>The falling edge is effective.<br>The pulse width is 1.28 us.                                                                                                                                                                                                                                                               | Н        |

| XTXTIM | 88   | I<br>5T | <b>Transmit Timing:</b><br>When using an external timing signal to start transmitting the frame in the running state, the cyclical trigger signal is required to input into XTXTIM. In this case, the register setting must be needed to switch from the internal timing signal that is default. XTXTIM is ignored out of the running state. The falling edge is effective.<br>When not using XTXTIM, connect to VDD(3.3 V). |          |

#### Clock and Reset:

| Name           | Pin#     | Туре     | Description                                                                                                                                                                                                                                                                                            |

|----------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

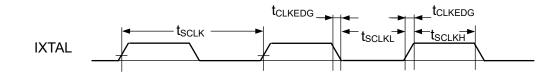

| OXTAL<br>IXTAL | 62<br>64 | I/O<br>I | <b>Crystal Output and Input for MII:</b><br>IXTAL must be driven with a 25 MHz oscillator clock that is the<br>same as driving PHY chip. Accuracy is +/- 50 ppm.<br>OXTAL must be left unconnected.<br>A dumping register that is about 33 Ohm should be put near<br>the output pin of the oscillator. |

| XRST           | 80       | І<br>5Т  | Reset input:<br>Hardware reset input. Low active.                                                                                                                                                                                                                                                      |

# JTAG(Boundary Scan):

These pins are for factory test only. For normal operation, these pins cannot be used.

| Name | Pin# | Туре            | Description                                 |  |

|------|------|-----------------|---------------------------------------------|--|

| TCK  | 77   | I <sub>PU</sub> | JTAG Clock:                                 |  |

|      |      |                 | JTAG clock input.                           |  |

|      |      |                 | This pin should be connected to VDD(3.3 V). |  |

| TRST | 82   | I <sub>PU</sub> | JTAG Reset:                                 |  |

|      |      |                 | JTAG reset input. Low active.               |  |

|      |      |                 | This pin should be connected to GND.        |  |

| TMS  | 84   | I <sub>PU</sub> | JTAG Mode Select:                           |  |

|      |      |                 | JTAG mode select input.                     |  |

|      |      |                 | This pin should be connected to VDD(3.3 V). |  |

| TDI  | 83   | I <sub>PU</sub> | JTAG Data Input:                            |  |

|      |      |                 | JTAG data input.                            |  |

|      |      |                 | This pin should be connected to VDD(3.3 V). |  |

| TDO  | 94   | 0               | JTAG Data Output:                           |  |

|      |      |                 | JTAG data output.                           |  |

|      |      |                 | This pin must be left unconnected.          |  |

#### Power:

| Name   | Pin#                              | Туре | Description                                                                                      |

|--------|-----------------------------------|------|--------------------------------------------------------------------------------------------------|

| VDD    | 3,28,<br>53,78                    |      | $V_{DD}$ =3.3 V<br>Put decoupling ceramic-capacitors between VDD and VSS pairs close to MNM1221. |

| VSS    | 4,15,29,<br>40,54,<br>65,79<br>90 |      | V <sub>SS</sub> =GND                                                                             |

| ADDVDD | 16,33,<br>39,46,<br>56,63,<br>89  |      | $V_{DD}$ =3.3 V<br>Put decoupling ceramic-capacitors between VDD and VSS pairs close to MNM1221. |

| ADDVSS | 44,51,<br>61,81                   |      | V <sub>SS</sub> =GND                                                                             |

| IVPD   | 57                                | I    | IVPD must be connected directly to GND.<br>This is for an internal protection of the chip.       |

# **Slave Pin Descriptions**

The pins having the different functions from in master are described as follows:

#### Mode:

| Name            | Pin#     | Туре                                     | Description                                                                                                     |

|-----------------|----------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| MODE1,<br>MODE0 | 59<br>58 | I <sub>PD</sub><br>I <sub>PD</sub><br>5T | <b>Mode Selection:</b><br>The operating mode is set.<br>See "Operating Mode Settings".                          |

| BUSMODE         | 60       | I <sub>PD</sub><br>5T                    | Bus Mode Selection:<br>Data bus width (servo) or MAC-ID type (IN/OUT) is set.<br>See "Operating Mode Settings". |

#### **CPU interface:**

| Name            | Pin# | Туре | Description                                                                                                                                                                                          | At Reset |

|-----------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| XWAIT<br>/ XLED | 91   | 0    | Wait Request (Generic slave):<br>To ensure the access, XWAIT should be connected<br>to the wait input pin of the CPU.<br>Low active.                                                                 | Н        |

|                 |      |      | <b>LED output (IN or OUT slave):</b><br>In RUNNING state and not timeout, Low is outputted.<br>This signal is used for driving status LED. In addition,<br>the detection time of timeout is 20.9 ms. |          |

#### Timing signals:

| Name   | Pin# | Туре    | Description                                                                                                                                                                                                                                                                    | At Reset |

|--------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| XSYNC  | 93   | 0       | Synchronizing Timing Pulse:<br>After all slaves receive the frame in RUNNING state,<br>this pin outputs negative pulse at the same time in all<br>slaves. In only RUNNING state, this signal is<br>outputted.<br>The falling edge is effective.<br>The pulse width is 1.28 us. | Н        |

| XINTRX | 92   | 0       | <b>Receiving Interrupt Pulse:</b><br>XINTRX is outputted at receiving the frame<br>completely.<br>The falling edge is effective.<br>The pulse width is 1.28 us.                                                                                                                | Η        |

| XTXTIM | 88   | І<br>5Т | <b>Transmit Timing:</b><br>Connect to VDD because of no function in slave mode.                                                                                                                                                                                                |          |

# **Operating Mode Settings**

MNM1221 reads MODE[1:0] and BUSMODE pins after reset, and sets the operating mode as following table. These pins must be connected to VDD or GND directly according to each operating mode. In addition, these pins are read only once after reset.

| MODE1 | MODE0 | BUSMODE | Operating<br>Mode | Data pins   | Address pins | Pin 91 |

|-------|-------|---------|-------------------|-------------|--------------|--------|

|       |       | L       | Master            | D[15:0]     | A[10:1]      |        |

|       | L     | Н       | Waster            | D[31:0]     | A[10:2]      | XWAIT  |

| L     | Н     | L       | Generic           | D[15:0]     | A[10:1]      | AWAII  |

|       | п     | Н       | Slave             | D[7:0]      | A[10:0]      |        |

|       |       | L       | IN                | D[31:0]     | A[4:0] (BIN) |        |

| н     | L     | Н       | Slave             | (IN fixed)  | A[5:0] (BCD) | XLED   |

|       | Н     | L       | OUT               | D[31:0]     | A[4:0] (BIN) | ALED   |

|       |       | Н       | Slave             | (OUT fixed) | A[5:0] (BCD) |        |

Notes:

• Unused pins should be connected as follows:

Data ...... Pulled down with 10 k Ohm. However, if OUT slave, it may be open. Address ... Connect to GND directly.

- In IN/OUT slave, the data bus behaves to input or output pins for external interface.

- In IN/OUT slave, the address bus behaves to MAC-ID inputs which are read only once after reset. Also, either BIN or BCD as data type is selected with BUSMODE pin.

- In IN/OUT slave, Pin91 performs as XLED pin.

- In OUT slave, Low is outputted until receiving the first valid data after reset. Therefore, the system that is in safety side when Low is outputted must be designed. Also, since the data bus becomes Hi-Z during reset, pull-down resistors of about 10 k Ohm must be added to make stable level.

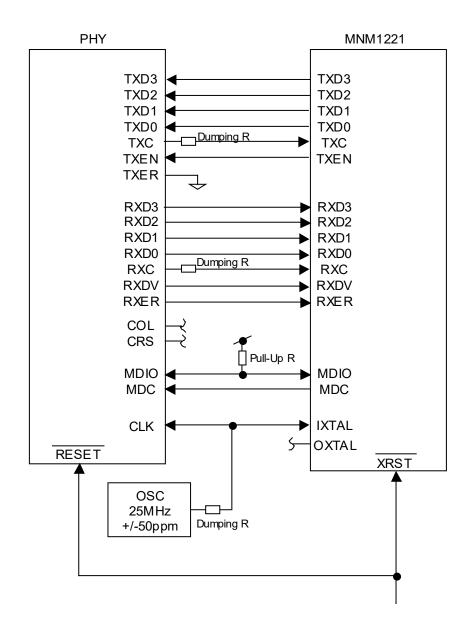

# **Connection to PHY with MII**

Notes:

- Approximately 33 Ohm is suitable for the dumping registers to reduce reflections.

- The value of the pull-up register on MDIO depends on PHY. It is approximately 1.5 k Ohm.

- The line length should be traced as short as possible.

# Chapter 2 Master Operation

# **Connection for Master Operation**

# Mode Setting

MNM1221 has two operating modes that are Master and Slave, and this document describes only Master mode. In Master mode, both MODE1 and MODE0 pins must be connected to GND.

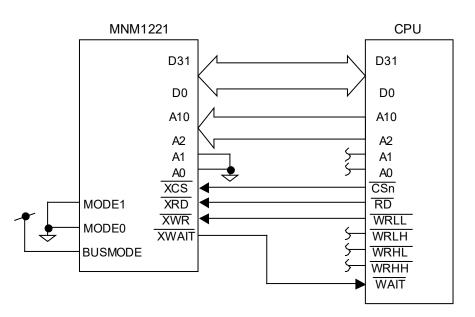

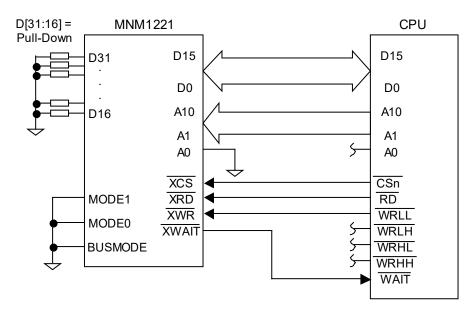

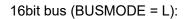

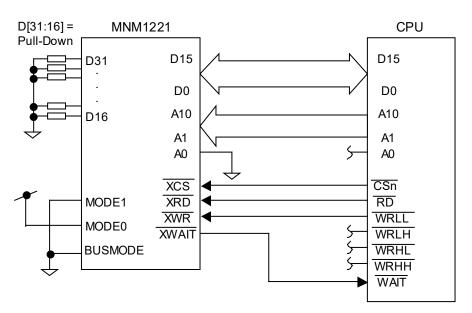

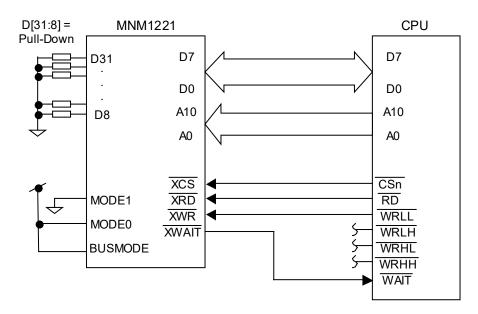

# Bus interface between MNM1221 and CPU

32 bits bus (BUSMODE = High):

16 bits bus (BUSMODE = Low):

Note: Approximately 10 k Ohm is suitable for the pull-down registers on D[31:16]. The above figure shows an example of CPU with byte-unit address bus.

# **Functional Description**

# State Transition of MNM1221

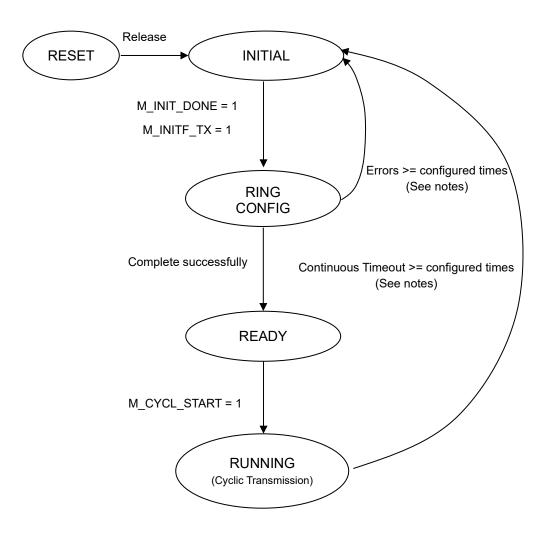

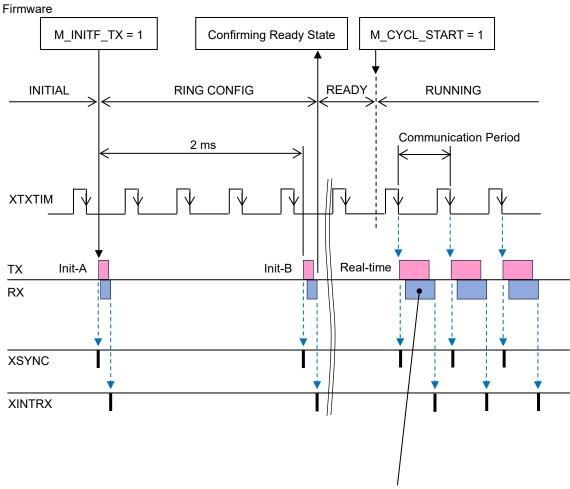

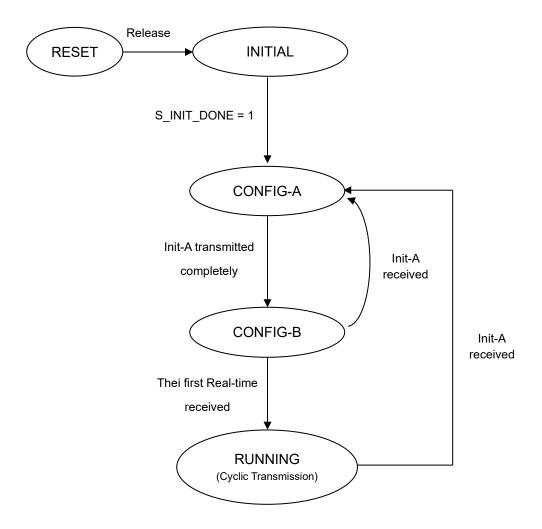

Before reaching RUNNING state that performs cyclic transmission, it goes through the process showed the following figure.

"M\_...": control registers

Notes:

- In RING CONFIG or RUNNING, M\_ERR\_COUNT configures the conditions changing to INITIAL.

- If M\_RESET is set to 1 in any state, the state becomes INITIAL.

# **Descriptions of Each State**

|           |                                                        | Commu     | nication |  |

|-----------|--------------------------------------------------------|-----------|----------|--|

| State     | Descriptions                                           | Frame     | Deried   |  |

|           |                                                        | Name      | Period   |  |

| INITIAL   | The firmware is initializing the registers in MNM1221. |           |          |  |

|           | e.g.) Transmitting period in RUNNING state             | -         | -        |  |

|           | MNM1221 is searching for the information about each    |           |          |  |

|           | Slave, and configuring the operation. As a result of   |           |          |  |

|           | the process, the information is stored into the status |           |          |  |

| RING      | registers.                                             | Init-A    |          |  |

| CONFIG    | e.g.) The sum of Slaves, MAC-IDs etc…                  | Init-B    | 2 ms     |  |

|           | For that, two initial frames are automatically         |           |          |  |

|           | transmitted.                                           |           |          |  |

|           | The firmware is waiting for READY state after finished |           |          |  |

|           | the process.                                           |           |          |  |

|           | MNM1221 is ready to proceed to RUNNING state.          |           |          |  |

| READY     | After checking the Slave information, the firmware     | -         | -        |  |

|           | instructs MNM1221 to proceed to RUNNING state.         |           |          |  |

|           |                                                        |           | XTXTIM   |  |

| RUNNING   | Using TX and RX memory in MNM1221,                     | Real-time | or       |  |

| DAIMINING | the firmware is communicating cyclically.              |           | Internal |  |

|           |                                                        |           | timer    |  |

#### Notes:

- In RING CONFIG state, using the internal timer, MNM1221 transmits the initial frames by itself.

If Slave is not established yet and Initial Error field in M\_ERR\_COUNT register is set to 0, the initial frame transmission is repeated.

- In READY state, the firmware confirms whether the sampled Slave information is the same as the intended one. If not, it must not proceed to RUNNING state.

# Frame Structure

|     | Init-A frame                   |         | Init-B frame     |

|-----|--------------------------------|---------|------------------|

|     | Preamble                       | 7-byte  | Preamble         |

|     | SFD                            | 1-byte  | SFD              |

|     | Frame ID                       | 2-byte  | Frame ID         |

|     | Check Code                     |         | Check Code       |

| _ = | Gathering<br>Slave Information | 66-byte | Setting to Slave |

|     | Error Marking                  | 4-byte  | Error Marking    |

|     | Frame CRC                      | 2-byte  | Frame CRC        |

|     | Dummy                          | 3-byte  | Dummy            |

Preamble: every 55h SFD: D5h Dummy: 00h

# Frame Descriptions

# Frame Types and Flow

There are three types of the frames: Init-A, Init-B and Real-time.

For each frame, the master transmits the frame first. When the first slave receives the frame, it writes data inside it and then transmits it. If multiple slaves are connected, the subsequent slaves will perform the same operation. Finally, the master receives the frame that all slaves have finished writing. The master is always the first to send a frame and the slaves never send frames voluntarily.

# Init-A, Init-B Frames

These frames are used in the RING CONFIG state. The master gathers the information about each slave with the Init-A frame, and the master sets control data to each slave with the Init-B frame.

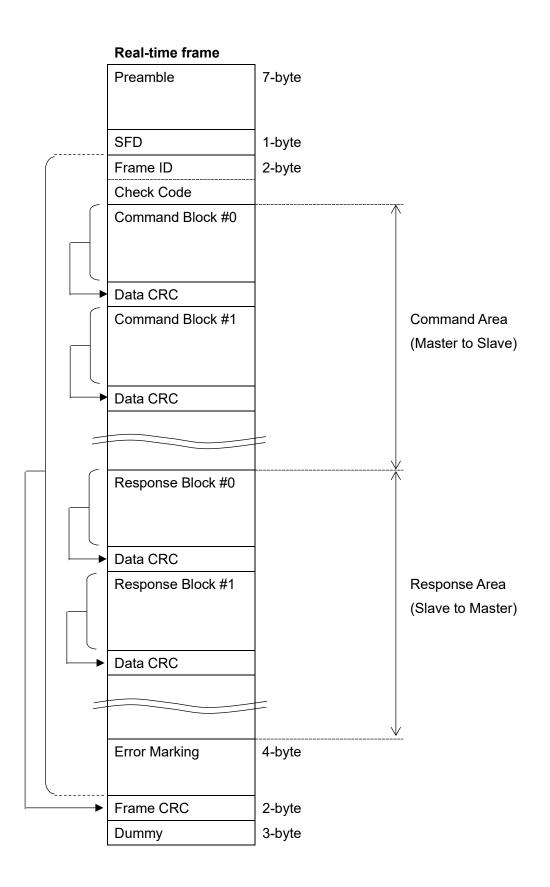

# Real-time Frame

This frame is used for data exchange between the master and the slaves in RUNNING state. The block which consists of 16 bytes is the unit of the exchange.

The inside of the frame is divided into areas for commands from the master to the slaves and responses from the slaves to the master. Inside each area, the data blocks occupied by each slave are arranged in the order of cable connection, first the blocks of the first slave, then the blocks of the second slave. The number of blocks each slave occupies is configured to range from 1 to 32, but there is a maximum limit of 32 blocks in an area. The frame length changes depending on the number of blocks in the area.

The command/response area in this frame corresponds to the TX/RX memory in MNM1221.

In the command area, after the master writes data to all blocks and sends it, each slave reads data from the block it occupies. In the response area, after the master sends data with an initial value of 0, each slave writes response data to the block it occupies. After receiving the frame, the master reads data from all blocks.

# Preamble, SFD (Start Frame Delimiter)

These are frame start codes specified by IEEE 802.3.

MNM1221 recognizes the beginning with Preamble 1-byte and SFD. Therefore, even if the Preamble is missing 6-byte, it can receive the frame normally. In the slave, the Preamble of the received frame is replaced with a new one before transmitting.

#### Frame ID

MNM1221 distinguishes the frame type with the Frame ID.

The Frame ID is inverted to the Check Code which is used to detect ID error.

|            | Init-A | Init-B | Real-time |

|------------|--------|--------|-----------|

| Frame ID   | 81h    | DBh    | 7Eh       |

| Check Code | 7Eh    | 24h    | 81h       |

#### **Discarding Frame**

The received frame is discarded in the following situations:

- An error is detected on the Frame ID.

- An interruption during reception makes the frame length shorter.

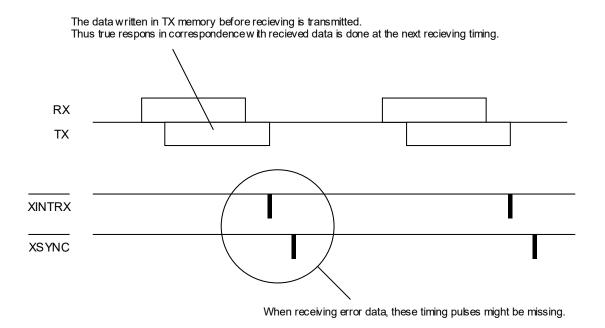

In this case, MNM1221 will not output XINTRX, and not output XSYNC on the slave either. In addition, since the slave does not transmit the frame, it is lost in subsequent nodes.

#### CRC

There are two CRCs, Frame CRC and Data CRC, based on the difference in the target area for detecting data error. The CRC specifications for both are as follows:

| Code                 | CRC-CCITT                   |

|----------------------|-----------------------------|

| Generator Polynomial | $X^{16} + X^{12} + X^5 + 1$ |

| Initial Value        | 0                           |

| Shift Direction      | Left                        |

### Frame CRC

The Frame CRC in every frame checks all data within the frame. Since some data always changes when the frame passes through the slave, it is replaced with a newly calculated Frame CRC at the same time.

#### **Error Marking**

If the slave detects a Frame CRC error when receiving a frame, it records the error in the Error Marking and then updates the Frame CRC. This notifies subsequent nodes that an error has been detected.

#### Data CRC

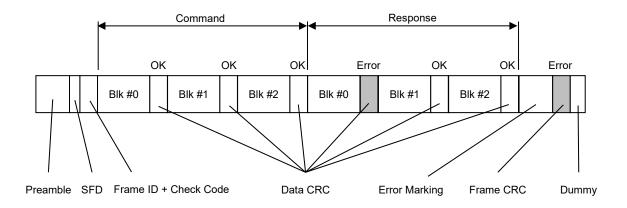

The Data CRC in the Real-time frame checks one block within the command or response area. When the frame passes through the slave, the response block occupied by that slave changes, so only the Data CRC of that part is replaced with the newly calculated one. Since the command block is only read by the slave and does not change, the Data CRC does not change either. The Data CRC is attached to each block, so if there are multiple blocks that partially show an error, the blocks that show OK can be used. For example, in the following figure which shows three blocks frame, the response block #0 cannot be used due to Data CRC error. However, the other blocks can be used since Data CRC shows OK. In addition, when the Data CRC shows error, ether the Frame CRC or the Error Marking shows error.

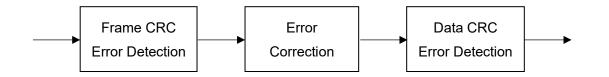

# Error Correction and CRC Error

MNM1221 has the error correction function, so even if the command/response blocks in the Realtime frame are corrupted, they will be automatically restored upon reception. However, there is a limit to the ability of this function, and if restoration is not possible, the Data CRC will show an error. On the other hand, since error detection using the Frame CRC checks the blocks before the error correction, it may happen that "All Data CRCs are OK, but Frame CRC is an error.". The blocks whose Data CRC indicates OK can be used regardless of the Frame CRC, so use only the Data CRC to determine usability.

### Dummy

The Dummy is used by MNM1221 for timing control.

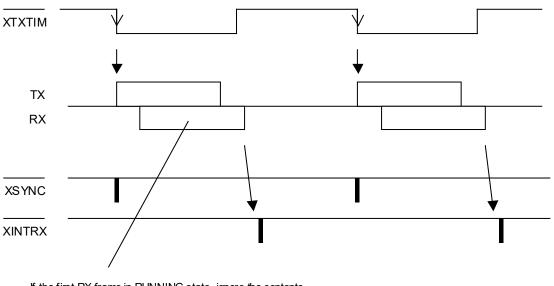

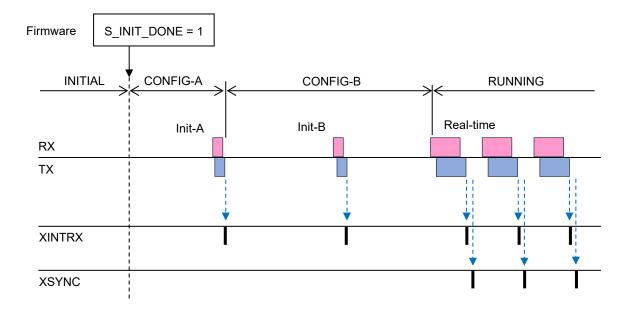

# Time Chart at Start-up

The following chart shows the case using XTXTIM for TX trigger in RUNNING state.

Ignore the contents of the first RX frame because of invalid data.

# Transmission in RUNNING State

#### Communication (Transmitting) Period:

Communication period, that is the same as transmitting period, can't be set up freely because it must be synchronized with servo control. According to servo specifications, the period must be set to suitable value as accurately as possible. In servo A6N, the communication period must be selected from 2 ms, 1 ms, 0.5ms, 0.25 ms, 0.125 ms, and 0.0625 ms. The command update period is the same or twice as the communication period. The default setting of the servo is that the communication period is 0.5 ms and the command update period is 1 ms.

#### Default setting of the servo:

| Communication period (Frame transmitting period) | 0.5 ms |

|--------------------------------------------------|--------|

| Command update period (Command is on the frame.) | 1 ms   |

#### **Timing Signals:**

The trigger for the cyclic data transmitting is selectable from two of a method, either an external timer signal to XTXTIM or the internal timer of MNM1221. The selection of trigger should be taken into the consideration of system structure. In general, it will be simple way to input the external timer signal because the synchronism with the NC operation is necessary for the timing. When selecting to use the internal timer, it will be necessary to synchronize the NC operation with the negative pulse output from XSYNC at the transmitting.

If not in RUNNING state or using the internal timer, XTXTIM input is ignored.

Also, XINTRX at completed receiving are outputted as timing signal to indicate to be able to access RX memory.

Note: The Low or High width of XTXTIM must keep minimum 1 us.

#### **Basic Operation:**

In running state, basically, when the command data written into TX memory is transmitted, the corresponding response data from Slaves will be received into RX memory.

Since the frame transmitting by Master makes Slave transmit the frame, the pair of TX and RX is corresponding as the physical frame. But note that the logical contents of the frame have time differential. Because there is no time that the firmware of Slave replies after interpreting the command in TX frame. Thus, as the logical contents, there is the response delay of at least one communication period. For example, an echo back data will be replied after one period. Particularly, the contents of the first RX frame must be ignored because there is no corresponding TX frame as logical.

If the first RX frame in RUNNING state, ignore the contents because ot invalid data.

Note:

If RX frame is not received by the next transmitting timing, Timeout bit on M\_ERR\_FLAGS2 register will be set.

# TX and RX Memory in MNM1221

A MNM1221 transmission buffer memory (TX memory) and reception buffer memory (RX memory) are respectively composed of 2 banks. To avoid conflict of data access, one bank is dedicated to the external CPU and another bank is dedicated to the internal communication module. And such assignment of the 2 banks is switched alternately.

#### Switching of banks:

|           | The trigger of switching        | Deferred switching |

|-----------|---------------------------------|--------------------|

| TX memory | M_TXMEM_SW = 1                  | Poing transmitted  |

|           | (This register is self cleared) | Being transmitted  |

| RX memory | Receiving completion            | M_RXMEM_HOLD = 1   |

Notes:

- For transmitting, M\_TXMEM\_SW must be set to 1 after writing the data.

- At least once before reading the received data, M\_RXMEM\_HOLD must be set to 0 to allow switching the bank. While reading the data, M\_RXMEM\_HOLD must be set to 1 to prevent the switching.

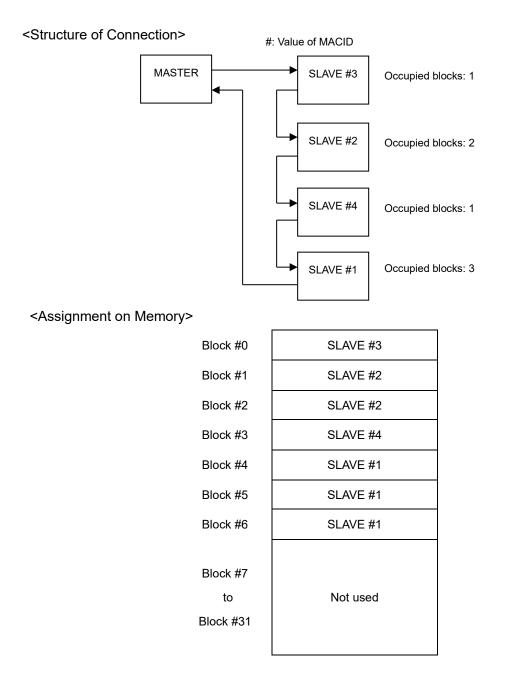

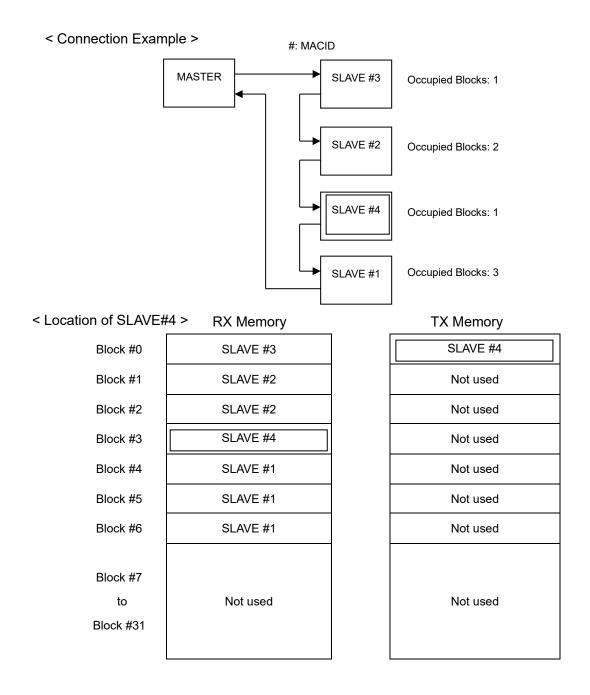

# Assignment on TX and RX Memory

The data of Slave nodes are arranged to on TX and RX memory in order of the cable connection. Since the arranging is from the lower block on the memory, the upper block area becomes empty if the sum of used blocks is less than 32.

The below figures show an example, there are Slave nodes that occupies plural blocks. But Slave normally occupies only one block.

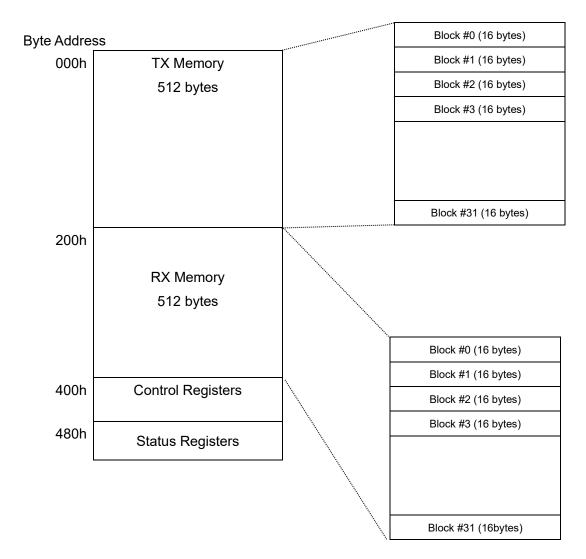

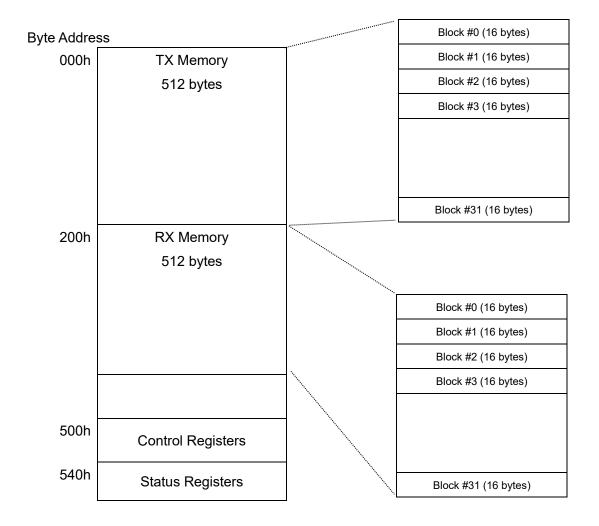

# **Memory Map**

Regardless of the bank switching, TX and RX memories are accessed with the same address.

#### Byte order:

"Little Endian" i.e. Lower data is in lower address.

| Byte Address | 4n | + 3 | 4n | + 2 | 4n + | + 1 | 4n | + 0 |

|--------------|----|-----|----|-----|------|-----|----|-----|

| Data         | 31 | 24  | 23 | 16  | 15   | 8   | 7  | 0   |

(n: 0, 1, 2, 3, ...)

# **Registers Description**

# Table of Registers

#### (1) Control Registers for Master

| Address | Name         | R/W | Default    |

|---------|--------------|-----|------------|

| 400h    | M_RESET      | W   | 0000 0000h |

| 404h    | M_INITF_TX   | R/W | 0000 0000h |

| 408h    | M_CYCL_START | R/W | 0000 0000h |

| 414h    | M_RTF_FORM   | R/W | 0000 0000h |

| 418h    | M_ERR_COUNT  | R/W | 0000 0333h |

| 41Ch    | M_INIT_DONE  | R/W | 0000 0000h |

| 420h    | M_TXTIM_SEL  | R/W | 0000 0000h |

| 424h    | M_TX_PERIOD  | R/W | 0000 C350h |

| 458h    | M_TXMEM_SW   | R/W | 0000 0000h |

| 45Ch    | M_RXMEM_HOLD | R/W | 0000 0000h |

## (2) Status Registers for Master

| Address | Name         | R/W | Default    |

|---------|--------------|-----|------------|

| 484h    | M_STATE      | R   | 0000 0008h |

| 488h    | M_INIT_ERR   | R   | 0000 0000h |

| 490h    | M_ERR_FLAGS1 | R   | 0000 0000h |

| 494h    | M_ERR_FLAGS2 | R   | 0000 0000h |

| 498h    | M_DCRC_ERR   | R   | 0000 0000h |

| 49Ch    | M_NODE_SUM   | R   | 0000 0000h |

| 4A0h    | M_BLK_SUM    | R   | 0000 0000h |

| 4A4h    | M_SINF_1_0   | R   | 0000 0000h |

| 4A8h    | M_SINF_3_2   | R   | 0000 0000h |

| 4ACh    | M_SINF_5_4   | R   | 0000 0000h |

| 4B0h    | M_SINF_7_6   | R   | 0000 0000h |

| 4B4h    | M_SINF_9_8   | R   | 0000 0000h |

| 4B8h    | M_SINF_11_10 | R   | 0000 0000h |

| 4BCh    | M_SINF_13_12 | R   | 0000 0000h |

| 4C0h    | M_SINF_15_14 | R   | 0000 0000h |

| 4C4h    | M_SINF_17_16 | R   | 0000 0000h |

| 4C8h    | M_SINF_19_18 | R   | 0000 0000h |

| 4CCh    | M_SINF_21_20 | R   | 0000 0000h |

| 4D0h    | M_SINF_23_22 | R   | 0000 0000h |

| 4D4h    | M_SINF_25_24 | R   | 0000 0000h |

| 4D8h    | M_SINF_27_26 | R   | 0000 0000h |

| 4DCh    | M_SINF_29_28 | R   | 0000 0000h |

| 4E0h    | M_SINF_31_30 | R   | 0000 0000h |

# Chip Reset

| Address | Name    | R/W | Default    |

|---------|---------|-----|------------|

| 400h    | M_RESET | W   | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -   |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0   |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | RST |

#### Bit 0: RST

When this bit is set to 1, MNM1221 will be reset.

It is the same as Low input into XRST pin.

Immediately after writing 1 to this register, it enters the reset state, so other registers cannot be accessed subsequently. Wait at least 10 us before the next operation.

| Bit 0 | Description                   |

|-------|-------------------------------|

| 0     | No operate                    |

| 1     | Reset MNM1221 (Self clearing) |

# **Initial Frame Transmit**

| Address | Name       | R/W | Default    |

|---------|------------|-----|------------|

| 404h    | M_INITF_TX | R/W | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | INF_TX |

## Bit 0: INF\_TX

When this bit is set to 1, MNM1221 proceeds to RING CONFIG state.

| Bit 0 | Description                            |

|-------|----------------------------------------|

| 0     | No operate                             |

| 1     | Transmit initial frame (Self clearing) |

# **Cyclic Transmission Start**

| Address | Name         | R/W | Default    |

|---------|--------------|-----|------------|

| 408h    | M_CYCL_START | R/W | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | CY_STA |

## Bit 0: CY\_STA

When this bit is set to 1, MNM1221 proceeds to RUNNING state.

| Bit 0 | Description                               |

|-------|-------------------------------------------|

| 0     | No operate                                |

| 1     | Start cyclic transmission (Self clearing) |

# Real-Time Frame Format

| Address | Name       | R/W | Default    |

|---------|------------|-----|------------|

| 414h    | M_RTF_FORM | R/W | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -   | -   |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0   |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | FM1 | FM0 |

## Bit [1:0]: FM[1:0]

You must set both bit0 and bit1 to 1.

| Bit1 | Bit0 | Description            |

|------|------|------------------------|

| 0    | 0    |                        |

| 0    | 1    | For manufacturing test |

| 1    | 0    |                        |

| 1    | 1    | Normal operation       |

# **Error Counter Setting**

| Address | Name        | R/W | Default    |

|---------|-------------|-----|------------|

| 418h    | M_ERR_COUNT | R/W | 0000 0333h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26      | 25    | 24 | 23  | 22      | 21     | 20   | 19 | 18 | 17           | 16   |

|----|----|----|----|----|---------|-------|----|-----|---------|--------|------|----|----|--------------|------|

| -  | -  | -  | -  | -  | -       | -     | -  | -   | -       | -      | -    | -  | -  | -            | -    |

| 15 | 14 | 13 | 12 | 11 | 10      | 9     | 8  | 7   | 6       | 5      | 4    | 3  | 2  | 1            | 0    |

| -  | -  | -  | -  |    | Initial | Error |    | Con | itinuou | ıs Tim | eout | Co |    | ous CF<br>RR | SC . |

Normally this register is set to 0, because errors are detected by firmware without using these error counters.

#### Bit [11:8]: Initial Error

|         | Description                                                       |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------|--|--|--|--|--|--|

| 0       | Disable the error counter.                                        |  |  |  |  |  |  |

| 0       | MNM1221 continues the ring configuration until pass successfully. |  |  |  |  |  |  |

| 1 to 15 | If initializing errors occur over the number of this value,       |  |  |  |  |  |  |

| 1 10 15 | MNM1221 stops the ring configuration, and goes to INITIAL state.  |  |  |  |  |  |  |

## Bit [7:4]: Continuous Timeout

|         | Description                                                                  |  |  |  |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 0       | Disable the error counter.                                                   |  |  |  |  |  |  |  |  |  |

| 0       | MNM1221 is in RUNNING state forever.                                         |  |  |  |  |  |  |  |  |  |

| 1 to 15 | If continuous timeout in running state occurs over the number of this value, |  |  |  |  |  |  |  |  |  |

| 110 15  | MNM1221 goes to INITIAL state.                                               |  |  |  |  |  |  |  |  |  |

#### Bit [3:0]: Continuous CRC ERR

|                                   | Description                                                                    |  |  |  |  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 0                                 | Disable the error counter.                                                     |  |  |  |  |  |  |  |  |

| 0<br>The error flag is never set. |                                                                                |  |  |  |  |  |  |  |  |

| 1 to 15                           | If continuous CRC error in running state occurs over the number of this value, |  |  |  |  |  |  |  |  |

| 1 10 15                           | MNM1221 set the error flag to 1.                                               |  |  |  |  |  |  |  |  |

# Initializing Done

| Address | Name        | R/W | Default    |

|---------|-------------|-----|------------|

| 41Ch    | M_INIT_DONE | R/W | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | INI_DN |

## Bit 0: INI\_DN

This bit must be set to 1 before M\_INITF\_TX register is set to 1.

| Bit 0 | Description                                        |

|-------|----------------------------------------------------|

| 0     | No operate                                         |

| 1     | Set this bit to 1 after setting initial registers. |

# **Transmit Timing Select**

| Address | Name        | R/W | Default    |

|---------|-------------|-----|------------|

| 420h    | M_TXTIM_SEL | R/W | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | TM_SEL |

#### Bit 0: TM\_SEL

Select timing clock for transmit in RUNNING state.

| Bit 0 | Description                     |

|-------|---------------------------------|

| 0     | Internal timer                  |

| 1     | External clock into XTXTIM pin. |

# **Transmission Period**

| Address | Name        | R/W | Default    |

|---------|-------------|-----|------------|

| 424h    | M_TX_PERIOD | R/W | 0000 C350h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25   | 24     | 23     | 22    | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|------|--------|--------|-------|----|----|----|----|----|----|

| -  | -  | -  | -  | -  | -  | -    | -      | -      | -     | -  | -  | -  | -  | -  | -  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8      | 7      | 6     | 5  | 4  | 3  | 2  | 1  | 0  |

|    |    |    |    |    |    | Trar | nsmiss | ion Pe | eriod |    |    |    |    |    |    |

#### Bit [15:0]: Transmission Period

Set transmission period in RUNNING state when using internal timer.

Period = 40[ns] x setting value

e.g.)

| Period  | Setting value |

|---------|---------------|

| 1000 us | 61A8h         |

| 500 us  | 30D4h         |

| 250 us  | 186Ah         |

| 125 us  | 0C35h         |

Notes:

- The period cannot be set up freely because it must be synchronized with the servo control on Slave side. Refer to "Transmission in RUNNING state".

- It is not possible to set a period of 62.5 us to the internal timer, so in that case, use an external timer.

# **Transmission Memory Switch**

| Address | Name       | R/W | Default    |

|---------|------------|-----|------------|

| 458h    | M_TXMEM_SW | R/W | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | TXM_SW |

#### Bit 0: TXM\_SW

Switch transmission memory bank.

For transmission, this bit must be set to 1 after writing TX memory.

| Bit | : 0 | Description                           |

|-----|-----|---------------------------------------|

| 0   | )   | No operate                            |

| 1   |     | Switch TX memory bank (Self clearing) |

# **Receiving Memory Hold**

| Address | Name         | R/W | Default    |

|---------|--------------|-----|------------|

| 45Ch    | M_RXMEM_HOLD | R/W | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | RXM_HD |

#### Bit 0: RXM\_HD

While this bit is set to 1, receiving memory bank is not switched. If received in such a period, the switching is deferred until clearing to 0.

| Bit 0 | Description                    |  |  |  |  |  |

|-------|--------------------------------|--|--|--|--|--|

| 0     | nable switching RX memory bank |  |  |  |  |  |

| 1     | Hold RX memory bank            |  |  |  |  |  |

# **Communication State**

| Address | Name    | R/W | Default    |

|---------|---------|-----|------------|

| 484h    | M_STATE | R   | 0000 0008h |

Bit fields:

| 31 | 30 | 29 | 28   | 27    | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16 |

|----|----|----|------|-------|----|----|----|----|----|----|----|----|----|-----|----|

| -  | -  | -  | -    | -     | -  | -  | -  | -  | -  | -  | -  | -  | -  | -   | -  |

| 15 | 14 | 13 | 12   | 11    | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0  |

|    |    |    | Fran | ne ID |    |    |    | -  | -  | -  | -  |    | St | ate |    |

#### Bit [15:8]: Frame ID

Indicates the Frame ID in the received frame.

## Bit [3:0]: State

Indicates the MNM1221 state.

| Bit3 | Bit2 | Bit1 | Bit0 | State       |

|------|------|------|------|-------------|

| 1    | 0    | 0    | 0    | INITIAL     |

| 0    | 1    | 0    | 0    | RING CONFIG |

| 0    | 0    | 1    | 0    | READY       |

| 0    | 0    | 0    | 1    | RUNNING     |

|      | El   | se   |      | None        |

# Initializing Error

| Address | Name       | R/W | Default    |

|---------|------------|-----|------------|

| 488h    | M_INIT_ERR | R   | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

| -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | INI_ER |

#### Bit0: INI\_ER

When errors are detected over the number of the Initial error field in M\_ERR\_COUNT register at ring configuration, this bit becomes 1.

| Bit C | ) | Description                                         |

|-------|---|-----------------------------------------------------|

| 0     |   | Normal state                                        |

| 1     |   | Initializing error (Latched and Cleared after read) |

# Error Flags 1 (Errors at RING CONFIG)

| Address | Name         | R/W | Default    |

|---------|--------------|-----|------------|

| 490h    | M_ERR_FLAGS1 | R   | 0000 0000h |

Bit fields:

| 31 | 30            | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|---------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| -  | -             | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  |

| 15 | 14            | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | Error Flags 1 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

This register indicates errors at RING CONGIF state.

When an error is detected, each bit is latched to 1. After reading, it is cleared to 0.

#### Bit15: Init-B frame CRC-error 2

If the Error Marking in the Init-B frame indicates an error, this bit becomes 1.

#### Bit14: Init-B frame CRC-error 1

If the Frame CRC in the Init-B frame indicates an error, this bit becomes 1.

#### Bit13: Init-B frame ACK mismatch

If there is a slave that does not respond to the Init-B frame, this bit becomes 1.

#### Bit12: Init-B frame length short

If the length of the Init-B frame is short, this bit becomes 1.

#### Bit11: Not used

Ignore this bit.

## Bit10: Init-B frame ID error

If the Frame ID in the Init-B frame indicates an error, this bit becomes 1.

## Bit9: Init-B frame ID mismatch

If the Frame IDs do not match between sending and receiving the Init-B frames, this bit becomes 1.

When this bit is 1, Bit10 is also 1.

## Bit8: Init-B frame timeout

If the Init-B frame is not received within 2 ms after sending it, this bit becomes 1.

#### Bit7: Init-A frame CRC-error 2

If the Error Marking in the Init-A frame indicates an error, this bit becomes 1.

#### Bit6: Init-A frame CRC-error 1

If the Frame CRC in the Init-A frame indicates an error, this bit becomes 1.

#### Bit5: Init-A frame length short

If the length of the Init-A frame is short, this bit becomes 1.

#### Bit4: Init-A frame block sum error

If the sum of blocks is 0 or over 32, this bit becomes 1.

#### Bit3: Init-A frame node sum error

If the sum of nodes is 0 or over 32, this bit becomes 1.

#### Bit2: Init-A frame ID error

If the Frame ID in the Init-A frame indicates an error, this bit becomes 1.

#### Bit1: Init-A frame ID mismatch

If the Frame IDs do not match between sending and receiving the Init-A frames, this bit becomes

1. When this bit is 1, Bit2 is also 1.

#### Bit0: Init-A frame ID timeout

If the Init-A frame is not received within 2 ms after sending it, this bit becomes 1.

Note:

When any of Bit12, Bit[10:8], Bit5, or Bit[2:0] is 1, MNM1221 does not output XINTRX. If reading this register in an interrupt by XINTRX, these bits indicate the previous error.

# Error Flags 2 (Errors at RUNNING)

| Address | Name         | R/W | Default    |

|---------|--------------|-----|------------|

| 494h    | M_ERR_FLAGS2 | R   | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28            | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|---------------|----|----|----|----|----|----|----|----|----|----|----|----|

| -  | -  | -  | -             | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  |

| 15 | 14 | 13 | 12            | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| -  | -  |    | Error Flags 2 |    |    |    |    |    |    |    |    |    |    |    |    |

This register indicates errors at RUNNING state.

When an error is detected, each bit except Bit11 is latched to 1. After reading, it is cleared to 0. For decision whether received data is ok, M\_DCRC\_ERR should be used instead of this register.

#### Bit13: Frame length short

If the length of the frame is short, this bit becomes 1.

#### Bit12: MII RXER

If both RXER and RXDV of MII are "H", this bit becomes 1.

## Bit11: Real-time frame Data-CRC-error (OR of bits in M\_DCRC\_ERR register)

This bit is simply "OR" of all bits in M\_DCRC\_ERR, so, not latched and not cleared after reading.

#### Bit10: Real-time frame continuous CRC-error

The condition of this bit set is defined M\_ERR\_COUNT register.

## Bit9: Real-time frame CRC-error 2

If the Error Marking in the Real-time frame indicates an error, this bit becomes 1.

#### Bit8: Init-C frame CRC-error 2

Reserved (Always 0)

## Bit7: Init-B frame CRC-error 2

Reserved (Always 0)

#### Bit6: Real-time frame CRC-error 1

If the Frame CRC in the Real-time frame indicates an error, this bit becomes 1.

#### Bit5: Init-C frame CRC-error 1

Reserved (Always 0)

#### Bit4: Init-B frame CRC-error 1

Reserved (Always 0)

#### **Bit3: Frame ID mismatch**

If the Frame IDs do not match between sending and receiving frames, this bit becomes 1. When this bit is 1, Bit2 is also 1.

#### Bit2: Frame ID error

If the Frame ID in the frame indicates an error, this bit becomes 1.

#### **Bit1: Continuous timeout**

The condition of this bit set is defined M\_ERR\_COUNT register.

If this bit becomes 1, MNM1221 go to INITIAL state.

#### **Bit0: Timeout**

If RX not coming until the next TX timing, this bit becomes 1.

Note:

When any of Bit13, Bit3, Bit2, or Bit0 is 1, MNM1221 does not output XINTRX.

If reading this register in an interrupt by XINTRX, these bits indicate the previous error.

# Data CRC Errors

| Address | Name       | R/W | Default    |

|---------|------------|-----|------------|

| 498h    | M_DCRC_ERR | R   | 0000 0000h |

Bit fields:

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| #31 | #30 | #29 | #28 | #27 | #26 | #25 | #24 | #23 | #22 | #21 | #20 | #19 | #18 | #17 | #16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| #15 | #14 | #13 | #12 | #11 | #10 | #9  | #8  | #7  | #6  | #5  | #4  | #3  | #2  | #1  | #0  |

#### Bit n: #n

When Data CRC errors is detected in the block at RUNNING state, this bit becomes 1.

The bit number corresponds to the block number.

Normally, this register is used for decision whether received data is OK, and M\_ERR\_FLAGS2 is not used. Because there is the case that M\_ERR\_FLAGS2 shows errors but M\_DCRC\_ERR shows no errors by error correcting function of MNM1221. In such a case, the data can be used.

|   | Description                                              |

|---|----------------------------------------------------------|

| 0 | Normal state                                             |

| 1 | CRC error of data block (Latched and Cleared after read) |

# Slave Node Sum

| Address | Name       | R/W | Default    |

|---------|------------|-----|------------|

| 49Ch    | M_NODE_SUM | R   | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23             | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |

|----|----|----|----|----|----|----|----|----------------|----|----|----|----|----|----|----|--|

| -  | -  | -  | -  | -  | -  | -  | -  | -              | -  | -  | -  | -  | -  | -  | -  |  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7              | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |

| -  | -  | -  | -  | -  | -  | -  | -  | Slave Node Sum |    |    |    |    |    |    |    |  |

#### Bit [7:0]: Slave Node Sum

Indicates the sum of Slave nodes detected in RING CONFIG state.

# Data Block Sum

| Address | Name      | R/W | Default    |

|---------|-----------|-----|------------|

| 4A0h    | M_BLK_SUM | R   | 0000 0000h |

Bit fields:

| 31 | 30 | 29 | 28 | 27 | 26             | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----------------|----|----|----|----|----|----|----|----|----|----|

| -  | -  | -  | -  | -  | -              | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  |

| 15 | 14 | 13 | 12 | 11 | 10             | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| -  | -  | -  | -  | -  | Data Block Sum |    |    |    |    |    |    |    |    |    |    |

#### Bit [10:0]: Data Block Sum

Indicates the sum of Slave data blocks detected in RING CONFIG state.

# Slave Information

| Address | Name         | R/W | Default    |

|---------|--------------|-----|------------|

| 4A4h    | M_SINF_1_0   | R   | 0000 0000h |

| 4A8h    | M_SINF_3_2   | R   | 0000 0000h |

| 4ACh    | M_SINF_5_4   | R   | 0000 0000h |

| 4B0h    | M_SINF_7_6   | R   | 0000 0000h |

| 4B4h    | M_SINF_9_8   | R   | 0000 0000h |

| 4B8h    | M_SINF_11_10 | R   | 0000 0000h |

| 4BCh    | M_SINF_13_12 | R   | 0000 0000h |

| 4C0h    | M_SINF_15_14 | R   | 0000 0000h |

| 4C4h    | M_SINF_17_16 | R   | 0000 0000h |

| 4C8h    | M_SINF_19_18 | R   | 0000 0000h |

| 4CCh    | M_SINF_21_20 | R   | 0000 0000h |

| 4D0h    | M_SINF_23_22 | R   | 0000 0000h |

| 4D4h    | M_SINF_25_24 | R   | 0000 0000h |

| 4D8h    | M_SINF_27_26 | R   | 0000 0000h |

| 4DCh    | M_SINF_29_28 | R   | 0000 0000h |

| 4E0h    | M_SINF_31_30 | R   | 0000 0000h |

Bit fields:

- Bit [31:16] is for Slave#2n+1

- Bit [15:0] is for Slave#2n

- (n: 0, 1, 2, ... 15)

| 31  | 30  | 29               | 28     | 27 | 26 | 25 | 24 | 23 | 22 | 21               | 20 | 19     | 18       | 17 | 16 |  |

|-----|-----|------------------|--------|----|----|----|----|----|----|------------------|----|--------|----------|----|----|--|

| ACT | MOD | MODE[1:0] MAC-ID |        |    |    |    |    | -  | -  | Number of Blocks |    |        |          |    |    |  |

| 15  | 14  | 13               | 12     | 11 | 10 | 9  | 8  | 7  | 6  | 5                | 4  | 3      | 2        | 1  | 0  |  |

| ACT | MOD | E[1:0]           | MAC-ID |    |    |    |    | -  | -  |                  | 1  | Number | of Block | s  |    |  |

This register indicates the Slave information detected in RING CONFIG state.

## Bit 31, Bit 15: ACT

Indicates presence of the Slave node.

|   | Description                     |

|---|---------------------------------|

| 0 | Not detected                    |

| 1 | Presence (The Slave is active.) |

## Bit [30:29], Bit [14:13]: MODE[1:0]

Indicates a kind of the Slave node.

| MODE1 | MODE0 | Description   |

|-------|-------|---------------|

| 0     | 0     | None          |

| 0     | 1     | Generic slave |

| 1     | 0     | Input slave   |

| 1     | 1     | Output slave  |

## Bit [28:24], Bit [12:8]: MAC-ID (Node Address)

Indicates MAC-ID (0 to 31) of the Slave node.

Using this information, duplicate MAC-ID checking by firmware is needed before proceeding to RUNNING state.

## Bit [21:16], Bit [5:0]: Number of Blocks

Indicates the number of data blocks the Slave node occupies.

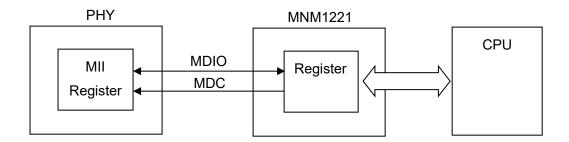

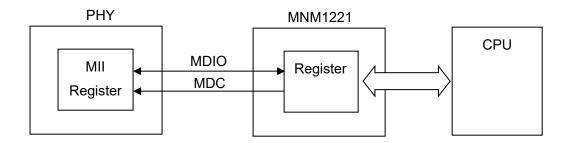

# **MII Register Access**

MNM1221 provides registers to access MII registers inside PHY chip.

In most PHY, this register access is not necessary since MNM1221 can perform properly with pin configuration only. But, some PHY such as KSZ8041 by Micrel needs the MII register setting as well. For the access, MDIO and MDC signals are used. See the following figure.

# Table of Registers

## (1) Control Registers

| Address | Name        | R/W | Default    |

|---------|-------------|-----|------------|

| 448h    | M_MDIO_WDAT | R/W | 0000 0000h |

| 44Ch    | M_MDIO_ADDR | R/W | 0000 0020h |

| 450h    | M_MDIO_WR   | R/W | 0000 0000h |

| 454h    | M_MDIO_RD   | R/W | 0000 0000h |

## (2) Status Register

| Address | Name        | R/W | Default    |