# System Design Guide for Master

Motor Business Unit Appliances Company

| Revision | Date      | Change Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 2005/7/14 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2        | 2012/1/31 | <ul> <li>P1 Changed title from "A Guide for Firmware Development".</li> <li>P3 Added introduction.</li> <li>P7 Added SH7216 example.</li> <li>P19 Added SH7145 example.</li> <li>P25 Added TMS320F28335 example.</li> <li>Deleted SH7065 example.</li> <li>Deleted TMS320VC33-120 example.</li> <li>P58 Added overview of profile position I/F.</li> <li>P72 Added internal-timer using system.</li> <li>Minor edits.</li> </ul> |

|          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### Introduction

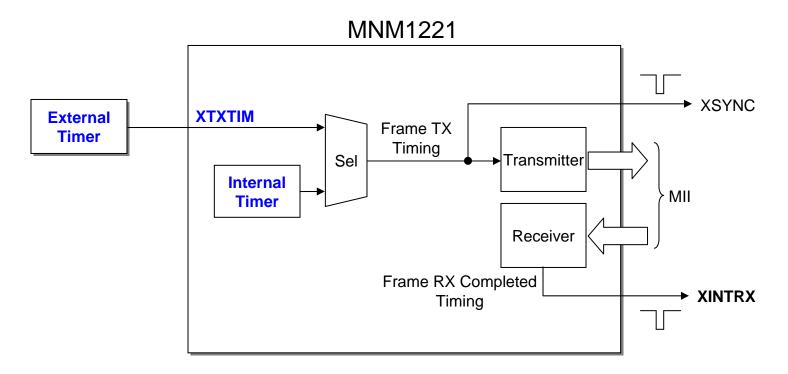

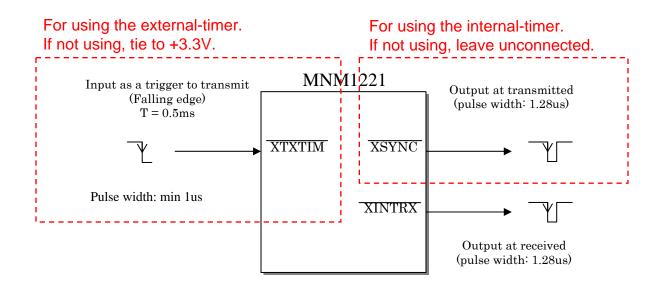

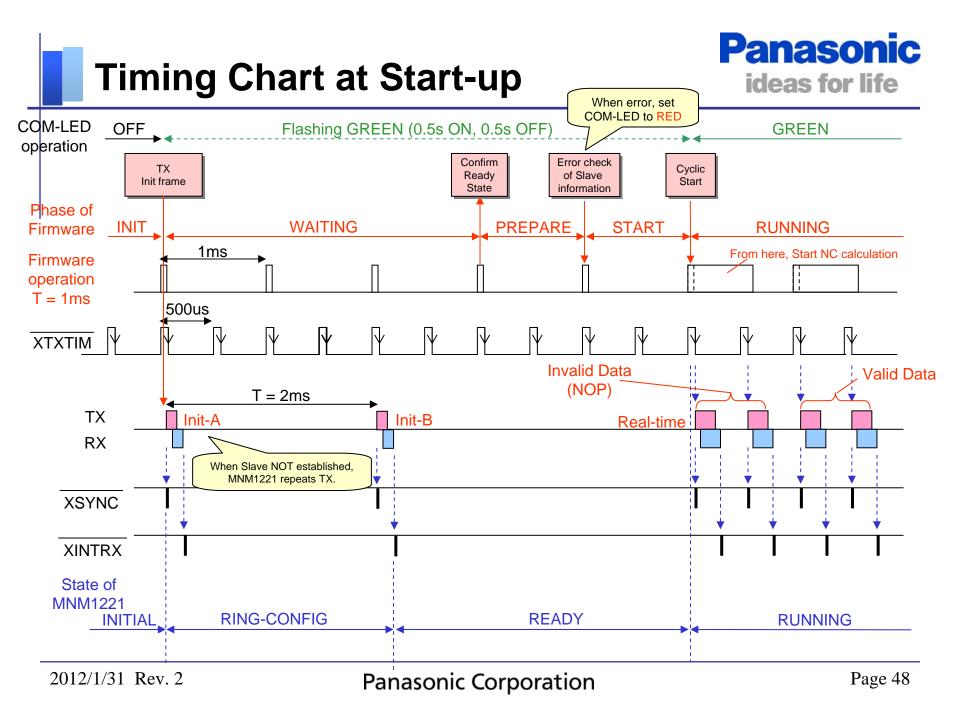

To control transmit-timing, MNM1221 has two timer sources that are an external-timer and an internal-timer.

This document describes examples of the external-timer using system in chapter 1, and the internal-timer using system in chapter 2.

## **Timing Signal Pins of MNM1221**

#### Note:

If not in RUNNING state, XTXTIM input is ignored.

Init-A and Init-B frame in RING-CONFIG state are automatically transmitted with internal timer of MNM1221.

Panasonic

ideas for life

# Chapter 1 External-Timer Using System

# **Goal of Timing Control**

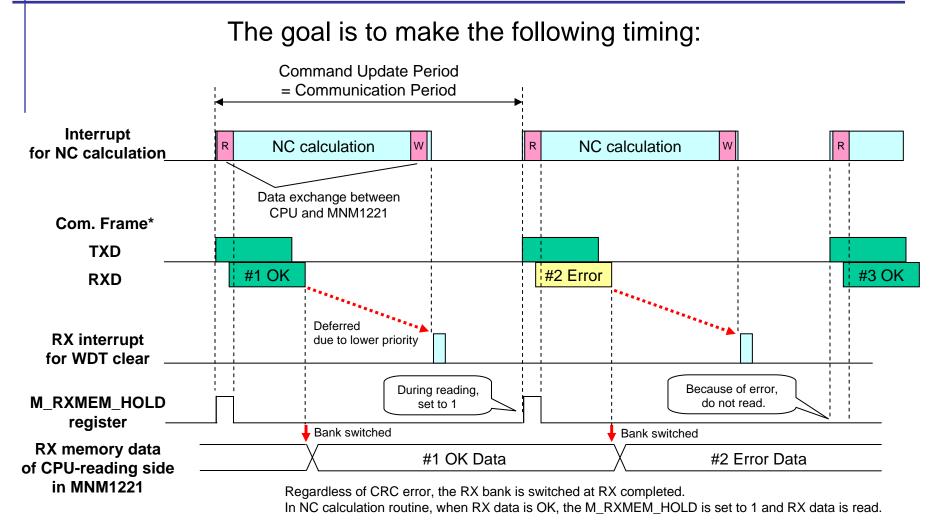

#### The goal is to make the following timing:

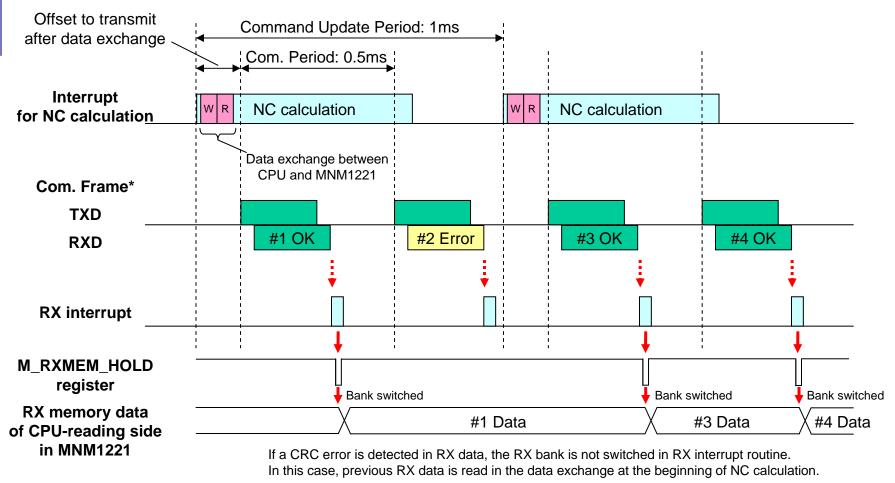

\* One frame contains data of all slave nodes, and its length depends on the number of connected nodes.

Panasonic Corporation

# Example for SH7216 (Renesas)

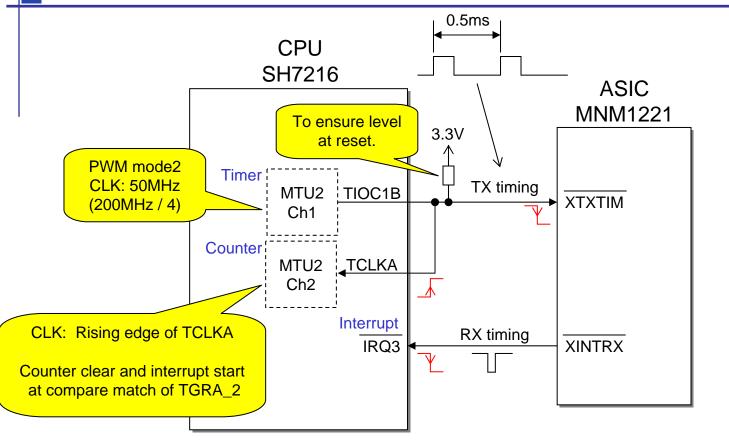

# **Timing Circuit**

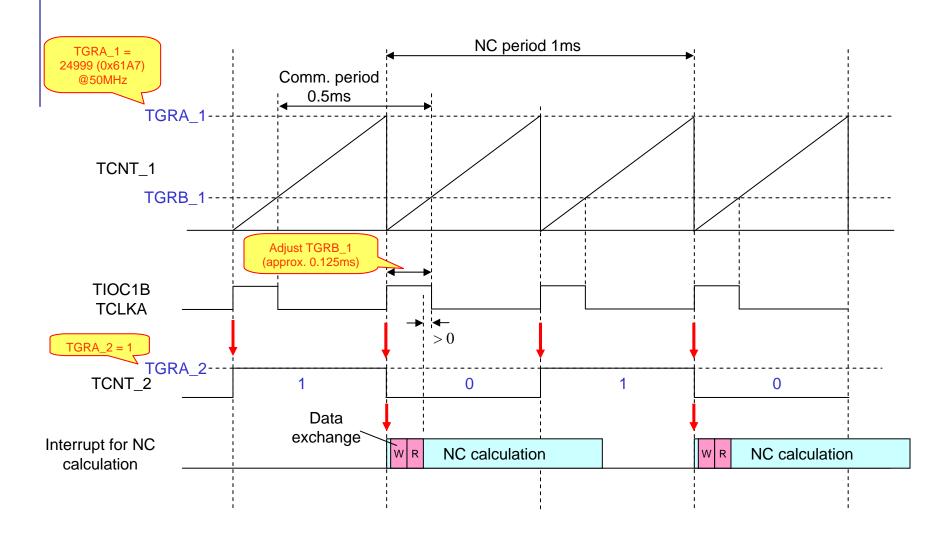

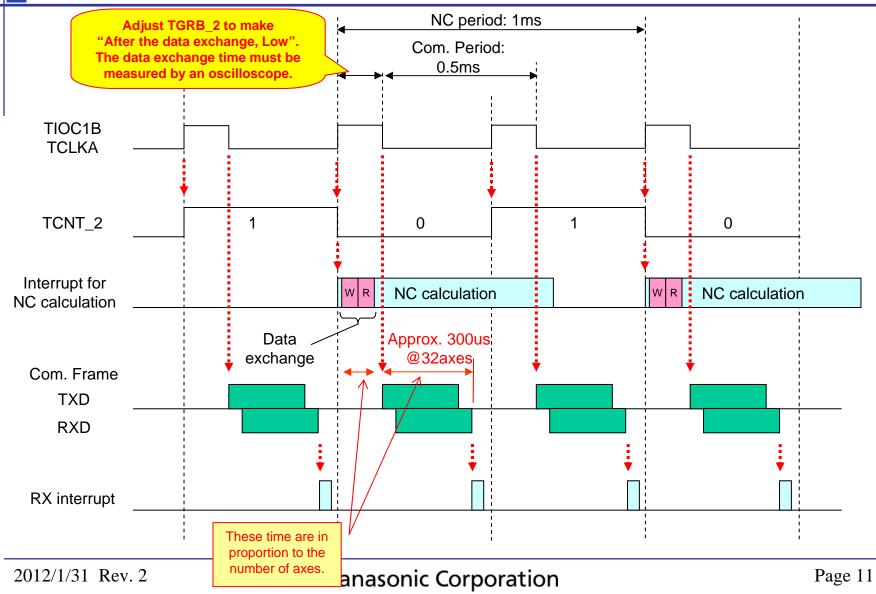

- MTU2-Ch1 generates TX timing signal. For 0.5ms, TGRA\_1 = 24999(0x61A7)@50MHz

- MTU2-Ch2 divides this signal, and generates the start signal for NC calculating interrupt. For 1ms, TGRA\_2 = 1

- IRQ3 by XINTRX of MNM1221 causes RX interrupt.

| Source | Trigger                      | Priority                 | Period | Operation                                                                     |

|--------|------------------------------|--------------------------|--------|-------------------------------------------------------------------------------|

| TGIA_2 | Compare match<br>of MTU2 Ch2 | -                        | 1ms    | <ul> <li>Communication data exchange</li> <li>NC calculation</li> </ul>       |

| /IRQ3  | RX complete                  | Higher<br>than<br>TGIA_2 | 0.5ms  | <ul> <li>Communication status check</li> <li>RX memory bank switch</li> </ul> |

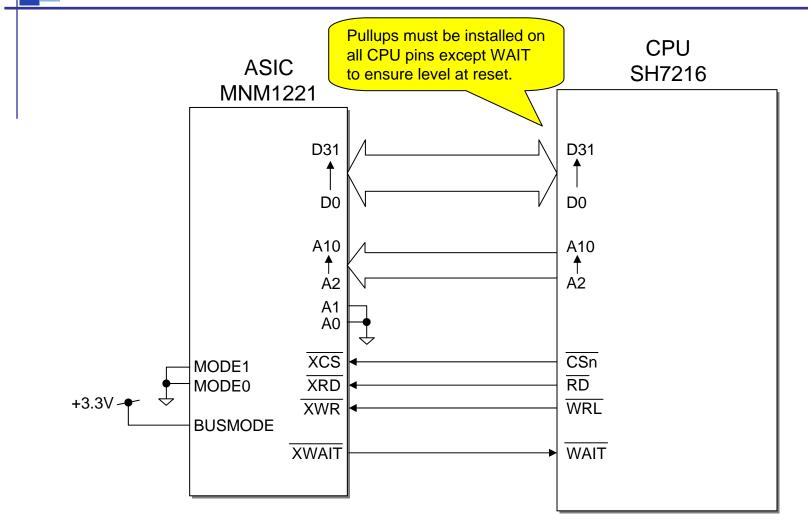

#### **Bus Connection**

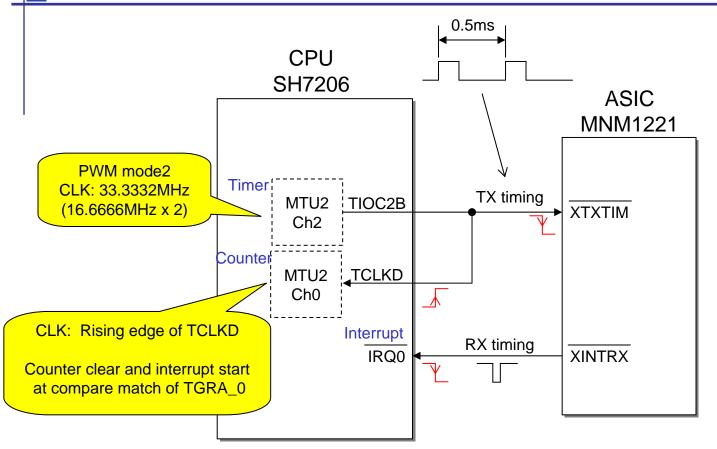

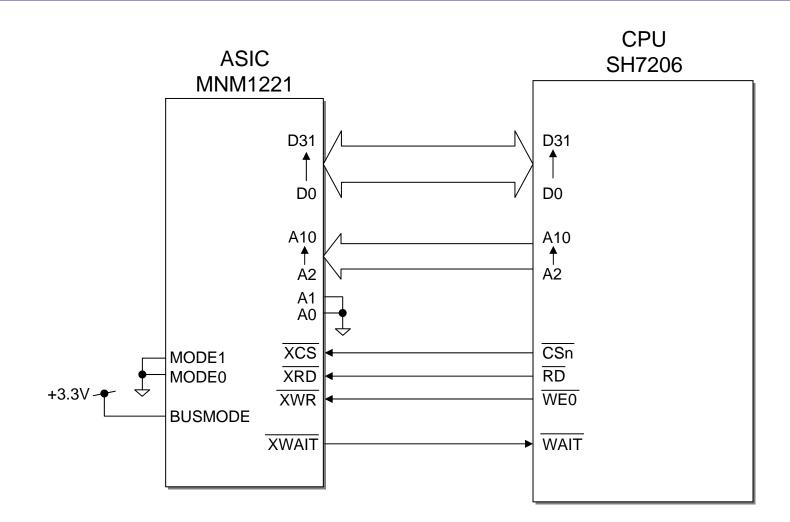

# Example for SH7206 (Renesas)

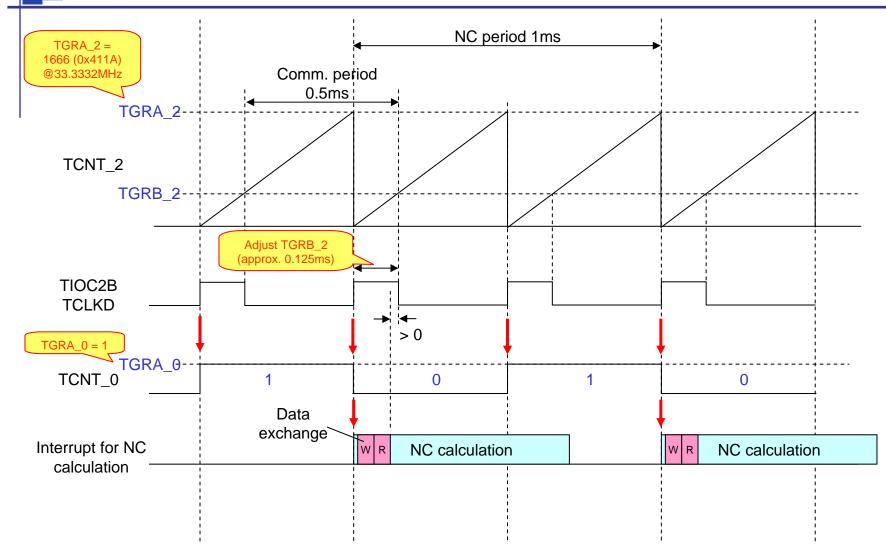

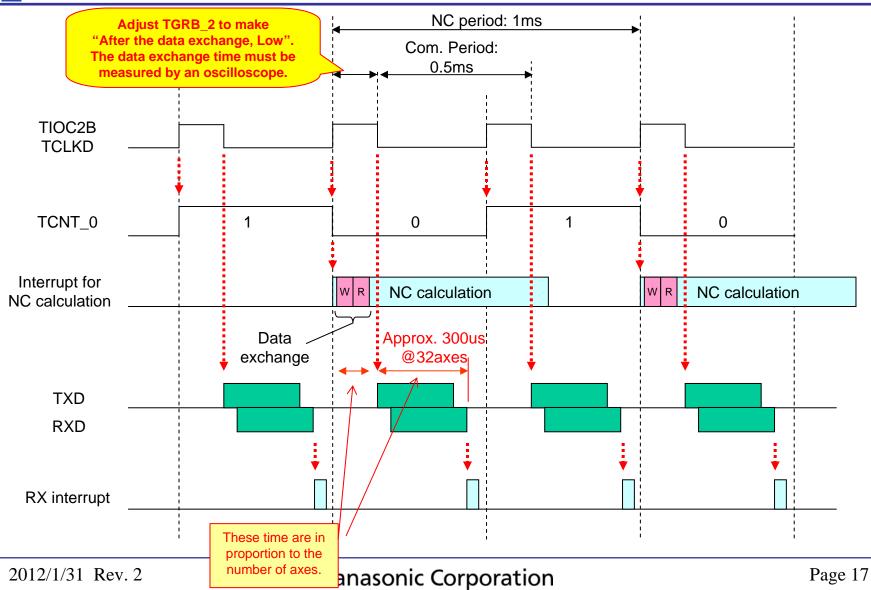

- MTU2-Ch2 generates TX timing signal. For 0.5ms, TGRA\_2 = 16666(0x411A)@33.3332MHz

- MTU2-Ch0 divides this signal, and generates the start signal for NC calculating interrupt. For 1ms, **TGRA\_0 = 1**

- IRQ2 by XINTRX of MNM1221 causes RX interrupt.

| Source | Trigger                              | Priority | Period | Operation                                                                     |

|--------|--------------------------------------|----------|--------|-------------------------------------------------------------------------------|

| TGIA_0 | Compare match<br>of MTU2 Ch0         | -        | 1ms    | <ul> <li>Communication data exchange</li> <li>NC calculation</li> </ul>       |

| /IRQ0  | RX complete Higher<br>than<br>TGIA_0 |          | 0.5ms  | <ul> <li>Communication status check</li> <li>RX memory bank switch</li> </ul> |

### **Bus Connection**

Note: Because each pin of SH7206 has "weak-keeper", it is not necessary to install external pullups on bus-interface pins.

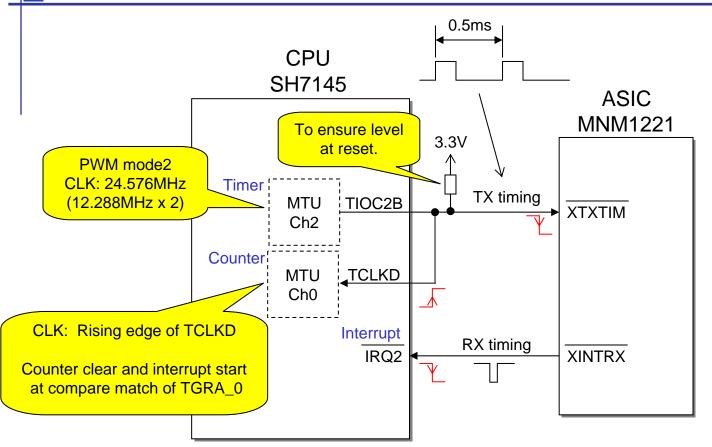

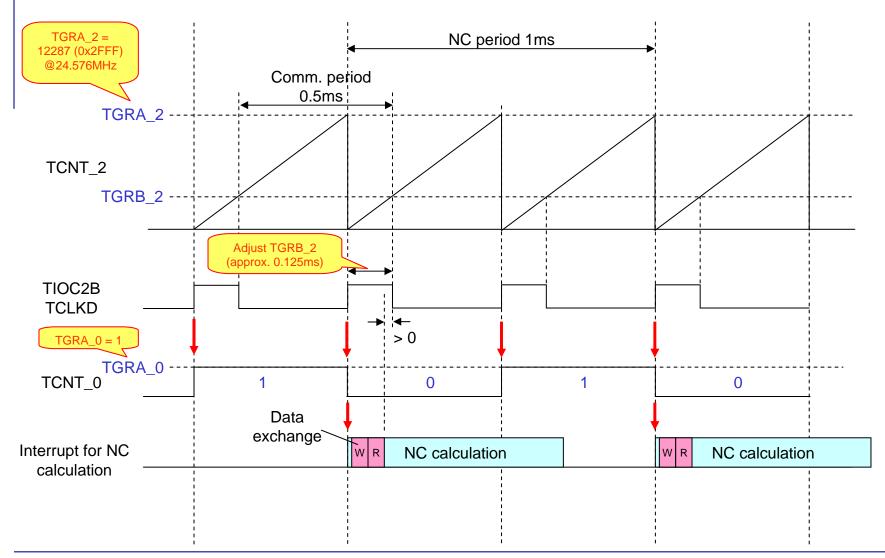

# Example for SH7145 (Renesas)

- MTU-Ch2 generates TX timing signal. For 0.5ms, TGRA\_2 = 12287(0x2FFF)@24.576MHz

- MTU-Ch0 divides this signal, and generates the start signal for NC calculating interrupt. For 1ms, TGRA\_0 = 1

- IRQ2 by XINTRX of MNM1221 causes RX interrupt.

| Source | Trigger                     | Priority                 | Period | Operation                                                                     |

|--------|-----------------------------|--------------------------|--------|-------------------------------------------------------------------------------|

| TGIA_0 | Compare match<br>of MTU Ch0 | -                        | 1ms    | <ul> <li>Communication data exchange</li> <li>NC Calculation</li> </ul>       |

| /IRQ2  | RX complete                 | Higher<br>than<br>TGIA_0 | 0.5ms  | <ul> <li>Communication status check</li> <li>RX memory bank switch</li> </ul> |

anasonic Corporation

Page 23

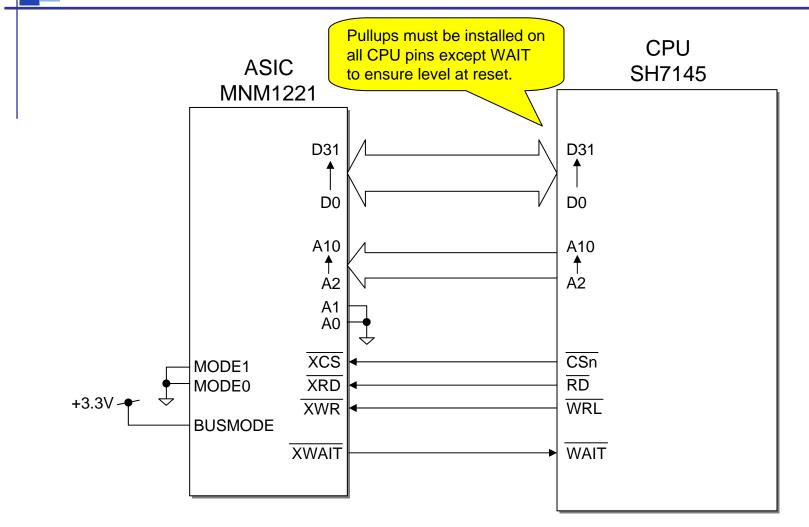

#### **Bus Connection**

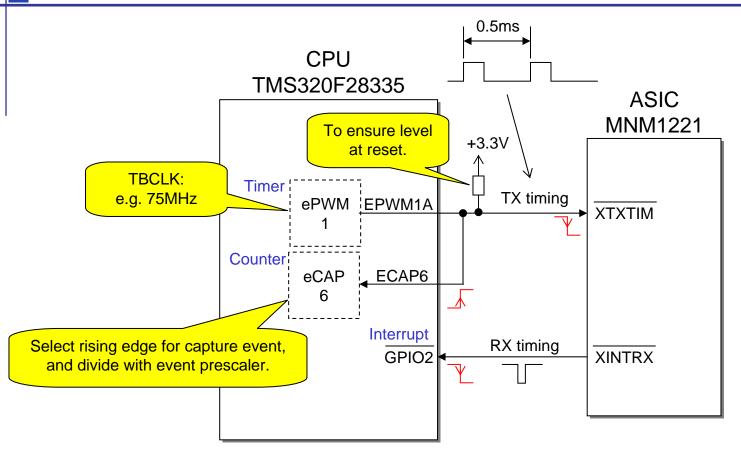

# Example for TMS320F28335 (TI)

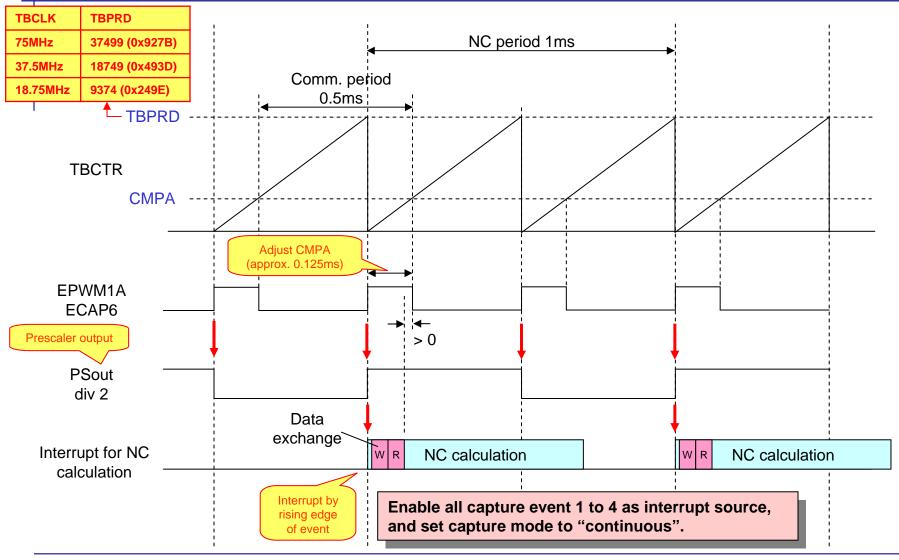

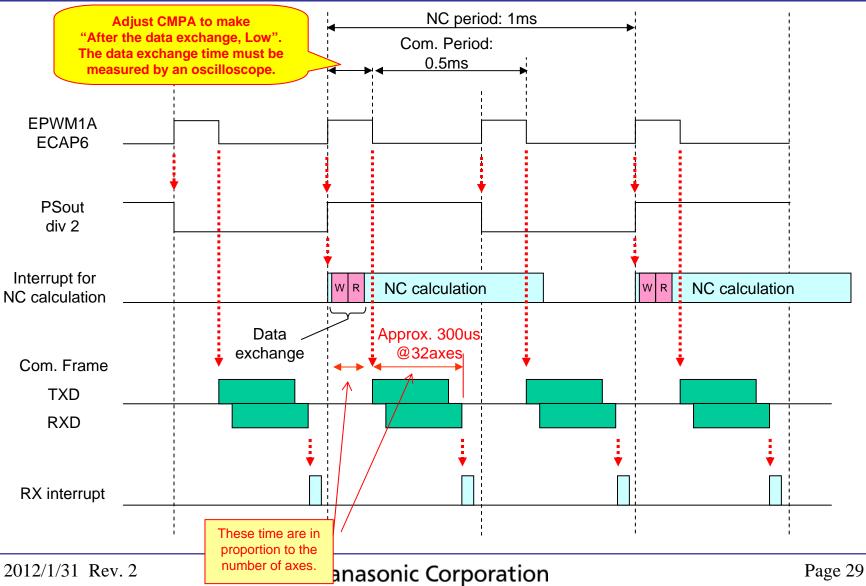

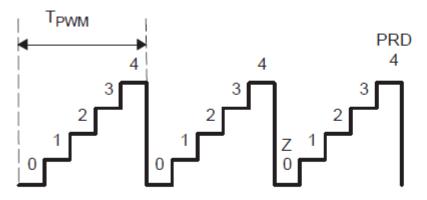

- ePWM1 generates TX timing signal. For 0.5ms, TBPRD = 37499(0x927B)@TBCLK 75MHz

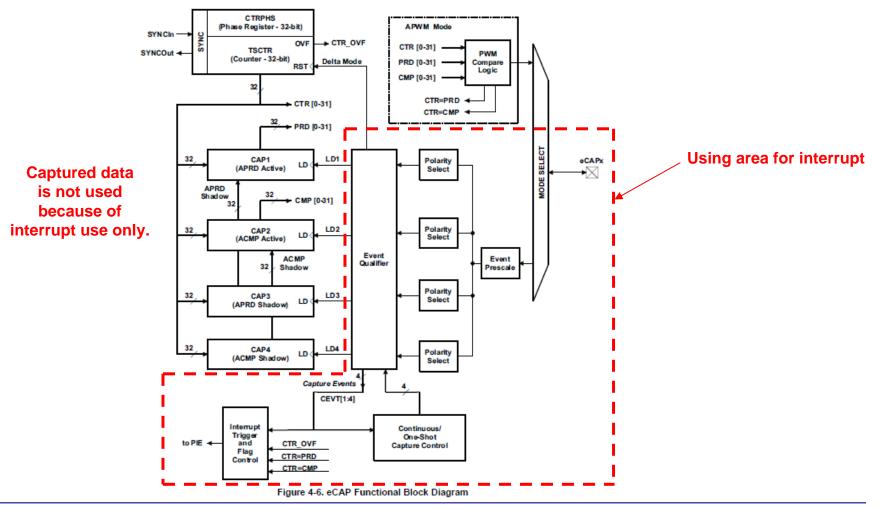

- eCAP6 divides this signal, and generates the start signal for NC calculating interrupt. For 1ms, **PRESCALE = 1**

- External interrupt by XINTRX through GPIO2 causes RX interrupt.

| Source                   | Trigger                   | Priority                | Period | Operation                                                                     |

|--------------------------|---------------------------|-------------------------|--------|-------------------------------------------------------------------------------|

| ECAP6<br>INT             | Capture event<br>of eCAP6 | -                       | 1ms    | <ul> <li>Communication data exchange</li> <li>NC calculation</li> </ul>       |

| XINT<br>through<br>GPIO2 | RX complete               | Higher<br>than<br>ECAP6 | 0.5ms  | <ul> <li>Communication status check</li> <li>RX memory bank switch</li> </ul> |

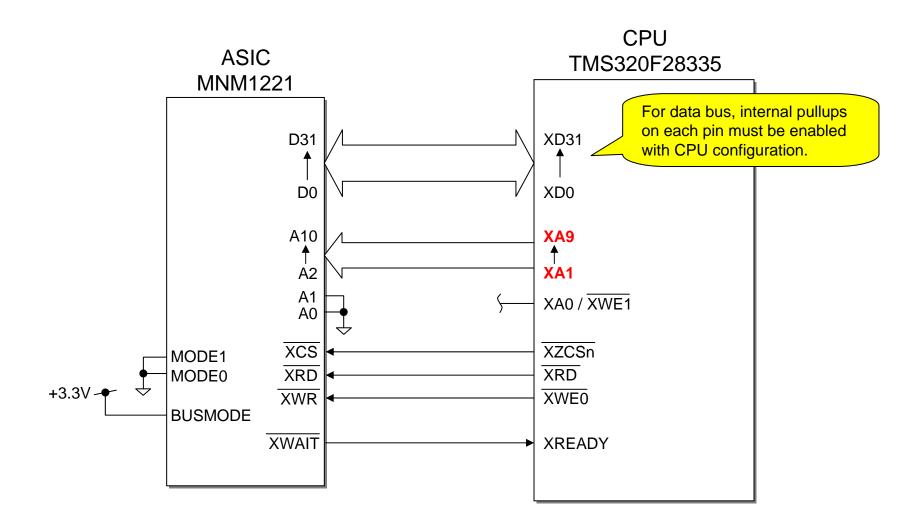

### **Bus Connection**

Note: TMS320F28335 has 16bit-unit address bus.

**Panasonic Corporation**

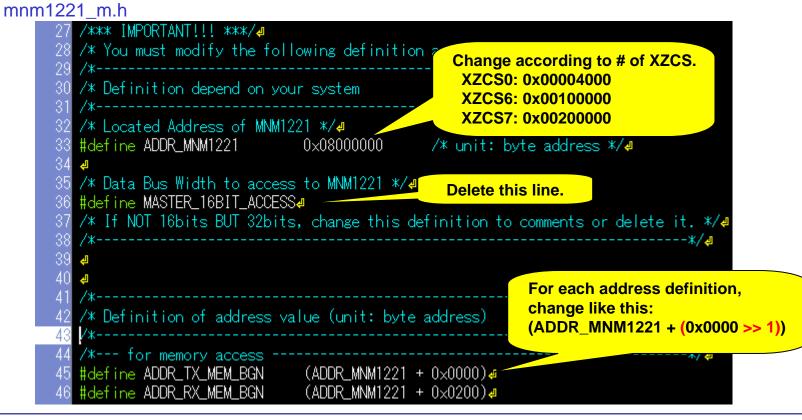

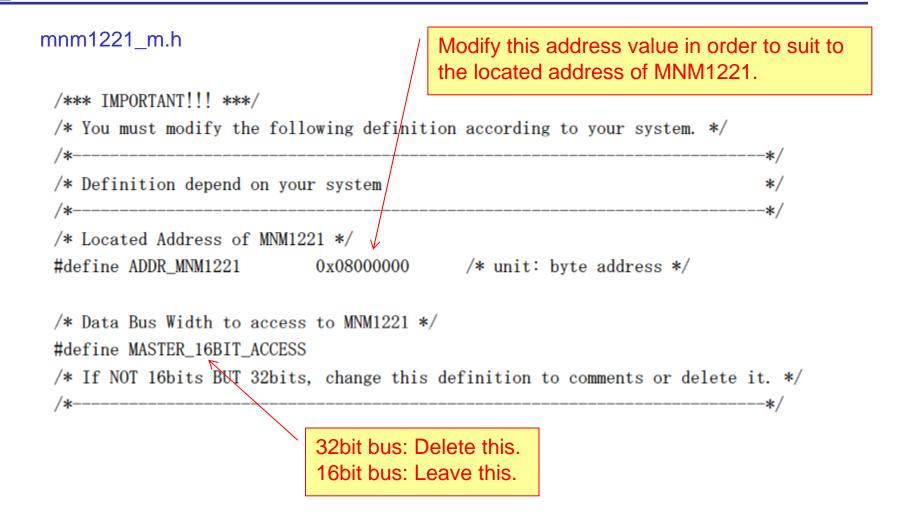

### **Important Notes for Address**

Although MNM1221 has 8bit-unit address bus, TMS320F28335 has 16bit-unit. Therefore each address connection must be shifted 1, such as A2(MNM1221) - XA1(TMS320F28335).

Also in the example code, all address definitions must be modified as follows:

# Details of TMS320F28335 Configuration

Figure 2-3. Time-Base Frequency and Period

Setting for 0.5ms:

| TBCLK                 | TBPRD          |

|-----------------------|----------------|

| 75MHz (150MHz / 2)    | 37499 (0x927B) |

| 37.5MHz (150MHz / 4)  | 18749 (0x493D) |

| 18.75MHz (150MHz / 8) | 9374 (0x249E)  |

For Up Count and Down Count T<sub>PWM</sub> = (TBPRD + 1) x T<sub>TBCLK</sub> F<sub>PWM</sub> = 1/ (T<sub>PWM</sub>)

TBCLK = SYSCLKOUT / (HSPCLKDIV × CLKDIV)

Panasonic

ideas for life

#### Interrupt by eCAP

#### 4.5 Enhanced CAP Modules (eCAP1/2/3/4/5/6)

The 2833x/2823x device contains up to six enhanced capture (eCAP) modules. Figure 4-6 shows a functional block diagram of a module.

2012/1/31 Rev. 2

Panasonic Corporation

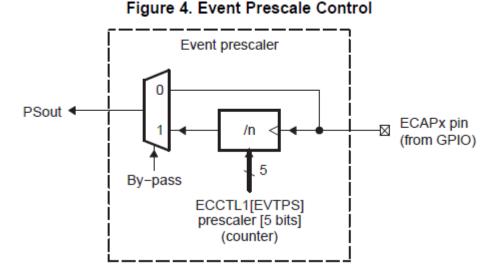

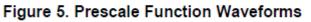

### **Event Prescaler inside eCAP**

A When a prescale value of 1 is chosen (i.e. ECCTL1[13:9] = 0,0,0,0,0 ) the input capture signal by-passes the prescale logic completely.

### **ECCTL1** Register

#### Table 7. ECAP Control Register 1 (ECCTL1) Field Descriptions

| Bit(s) | Field    | Value | Description                                            |

|--------|----------|-------|--------------------------------------------------------|

| 13:9   | PRESCALE |       | Event Filter prescale select                           |

|        |          | 00000 | Divide by 1 (i.e,. no prescale, by-pass the prescaler) |

|        |          | 00001 | Divide by 2                                            |

|        |          | 00010 | Divide by 4                                            |

|        |          | 00011 | Divide by 6                                            |

|        |          | 00100 | Divide by 8                                            |

|        |          | 00101 | Divide by 10                                           |

|        |          |       |                                                        |

|        |          | 11110 | Divide by 60                                           |

|        |          | 11111 | Divide by 62                                           |

| 6      | CAP4POL  |       | Capture Event 4 Polarity select                        |

|        |          | 0     | Capture Event 4 triggered on a rising edge (RE)        |

|        |          | 1     | Capture Event 4 triggered on a falling edge (FE)       |

| 4      | CAP3POL  |       | Capture Event 3 Polarity select                        |

|        |          | 0     | Capture Event 3 triggered on a rising edge (RE)        |

|        |          | 1     | Capture Event 3 triggered on a falling edge (FE)       |

| 2      | CAP2POL  |       | Capture Event 2 Polarity select                        |

|        |          | 0     | Capture Event 2 triggered on a rising edge (RE)        |

|        |          | 1     | Capture Event 2 triggered on a falling edge (FE)       |

| 0      | CAP1POL  |       | Capture Event 1 Polarity select                        |

|        |          | 0     | Capture Event 1 triggered on a rising edge (RE)        |

|        |          | 1     | Capture Event 1 triggered on a falling edge (FE)       |

#### Table 8. ECAP Control Register 2 (ECCTL2) Field Descriptions

| Bit(s) | Field       |   | Description                                                                                                                                                                                                                                                                                                                             |

|--------|-------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9      | 9 CAP/APWM  |   | CAP/APWM operating mode select                                                                                                                                                                                                                                                                                                          |

|        |             | 0 | <ul> <li>ECAP module operates in capture mode. This mode forces the following configuration:</li> <li>Inhibits TSCTR resets via CTR = PRD event</li> <li>Inhibits shadow loads on CAP1 and 2 registers</li> <li>Permits user to enable CAP1-4 register load</li> <li>CAPx/APWMx pin operates as a capture input</li> </ul>              |

|        |             | 1 | <ul> <li>ECAP module operates in APWM mode. This mode forces the following configuration:</li> <li>Resets TSCTR on CTR = PRD event (period boundary</li> <li>Permits shadow loading on CAP1 and 2 registers</li> <li>Disables loading of time-stamps into CAP1-4 registers</li> <li>CAPx/APWMx pin operates as a APWM output</li> </ul> |

| 0      | CONT/ONESHT |   | Continuous or one-shot mode control (applicable only in capture mode)                                                                                                                                                                                                                                                                   |

|        |             | 0 | Operate in continuous mode                                                                                                                                                                                                                                                                                                              |

|        |             | 1 | Operate in one-Shot mode                                                                                                                                                                                                                                                                                                                |

#### Table 9. ECAP Interrupt Enable Register (ECEINT) Field Descriptions

| Bits | Field    | Value | Description                                      |           |

|------|----------|-------|--------------------------------------------------|-----------|

| 15:8 | Reserved |       |                                                  |           |

| 7    | CTR=CMP  |       | Counter Equal Compare Interrupt Enable           |           |

|      |          | 0     | Disable Compare Equal as an Interrupt source     |           |

|      |          | 1     | Enable Compare Equal as an Interrupt source      |           |

| 6    | CTR=PRD  |       | Counter Equal Period Interrupt Enable            |           |

|      |          | 0     | Disable Period Equal as an Interrupt source      | ✓ Disable |

|      |          | 1     | Enable Period Equal as an Interrupt source       |           |

| 5    | CTROVF   |       | Counter Overflow Interrupt Enable                |           |

|      |          | 0     | Disabled counter Overflow as an Interrupt source |           |

|      |          | 1     | Enable counter Overflow as an Interrupt source   |           |

| 4    | CEVT4    |       | Capture Event 4 Interrupt Enable                 |           |

|      |          | 0     | Disable Capture Event 1 as an Interrupt source   |           |

|      |          | 1     | Capture Event 4 Interrupt Enable                 |           |

| 3    | CEVT3    |       | Capture Event 3 Interrupt Enable                 |           |

|      |          | 0     | Disable Capture Event 1 as an Interrupt source   |           |

|      |          | 1     | Enable Capture Event 1 as an Interrupt source    |           |

| 2    | CEVT2    |       | Capture Event 2 Interrupt Enable                 | Enable    |

|      |          | 0     | Disable Capture Event 1 as an Interrupt source   |           |

|      |          | 1     | Enable Capture Event 1 as an Interrupt source    |           |

| 1    | CEVT1    |       | Capture Event 1 Interrupt Enable                 |           |

|      |          | 0     | Disable Capture Event 1 as an Interrupt source   |           |

|      |          | 1     | Enable Capture Event 1 as an Interrupt source    |           |

| 0    | Reserved |       |                                                  |           |

### **ECCLR Register**

#### At the beginning of interrupt routine, interrupt flags must be cleared to prepare the next interrupt.

| Bits | Field     |   | Description                                                                                                              |

|------|-----------|---|--------------------------------------------------------------------------------------------------------------------------|

| 15:8 | Reserved  |   |                                                                                                                          |

| 7    | 7 CTR=CMP |   | Counter Equal Compare Status Flag                                                                                        |

|      |           | 0 | Writing a 0 has no effect. Always reads back a 0                                                                         |

|      |           | 1 | Writing a 1 clears the CTR=CMP flag condition                                                                            |

| 6    | CTR=PRD   |   | Counter Equal Period Status Flag                                                                                         |

|      |           | 0 | Writing a 0 has no effect. Always reads back a 0                                                                         |

|      |           | 1 | Writing a 1 clears the CTR=PRD flag condition                                                                            |

| 5    | CTROVF    |   | Counter Overflow Status Flag                                                                                             |

| 1    |           | 0 | Writing a 0 has no effect. Always reads back a 0                                                                         |

|      |           | 1 | Writing a 1 clears the CTROVF flag condition                                                                             |

| 4    | CEVT4     |   | Capture Event 4 Status Flag                                                                                              |

|      |           | 0 | Writing a 0 has no effect. Always reads back a 0                                                                         |

|      |           | 1 | Writing a 1 clears the CEVT3 flag condition.                                                                             |

| 3    | CEVT3     |   | Capture Event 3 Status Flag                                                                                              |

|      |           | 0 | Writing a 0 has no effect. Always reads back a 0.                                                                        |

|      |           | 1 | Writing a 1 clears the CEVT3 flag condition.                                                                             |

| 2    | CEVT2     |   | Capture Event 2 Status Flag                                                                                              |

|      |           | 0 | Writing a 0 has no effect. Alwavs reads back a 0.                                                                        |

|      |           | 9 | Writing a 1 clears the CEVT2 flag condition.                                                                             |

| 1    | CEVT1     |   | Capture Event 1 Status Flag                                                                                              |

| 1    |           | 0 | Writing a 0 has no effect. Always reads back a 0.                                                                        |

| 1    |           | 1 | Writing a 1 clears the CEVT1 flag condition.                                                                             |

| 0    | INT       | - | Global Interrupt Clear Flag                                                                                              |

|      |           | 0 | Writing a 0 has no effect. Always reads back a 0.                                                                        |

|      |           | 1 | Writing a 1 clears the INT flag and enable further interrupts to be generated if any<br>of the event flags are set to 1. |

#### Table 11. ECAP Interrupt Clear Register (ECCLR) Field Descriptions

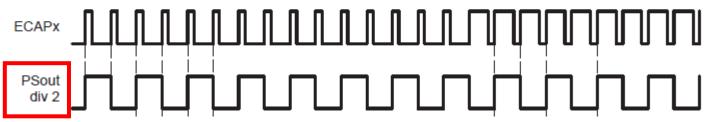

### **Capture Interrupt Sequence**

#### Interrupt occurring: CEVT1 $\rightarrow$ CEVT2 $\rightarrow$ CEVT3 $\rightarrow$ CEVT4 $\rightarrow$ CEVT1 $\rightarrow$ ...

#### Figure 22. Capture Sequence for Absolute Time-stamp and Rising Edge Detect

2012/1/31 Rev. 2

Panasonic Corporation

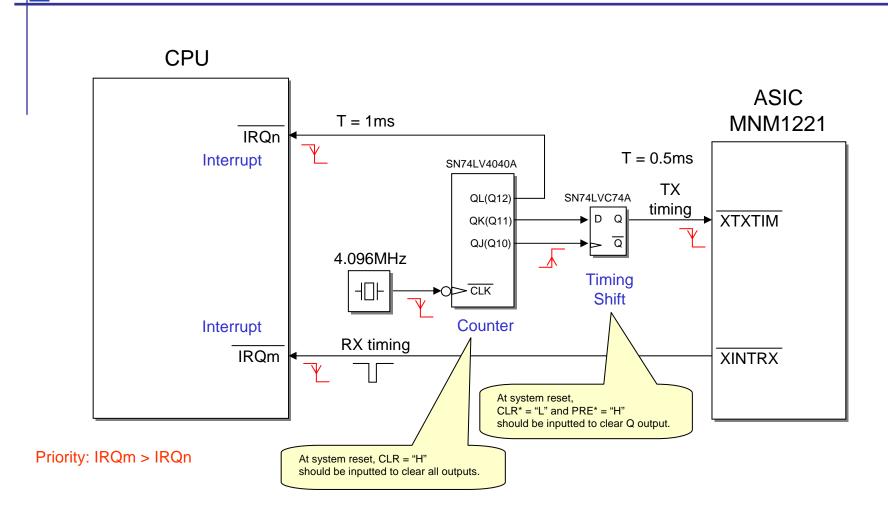

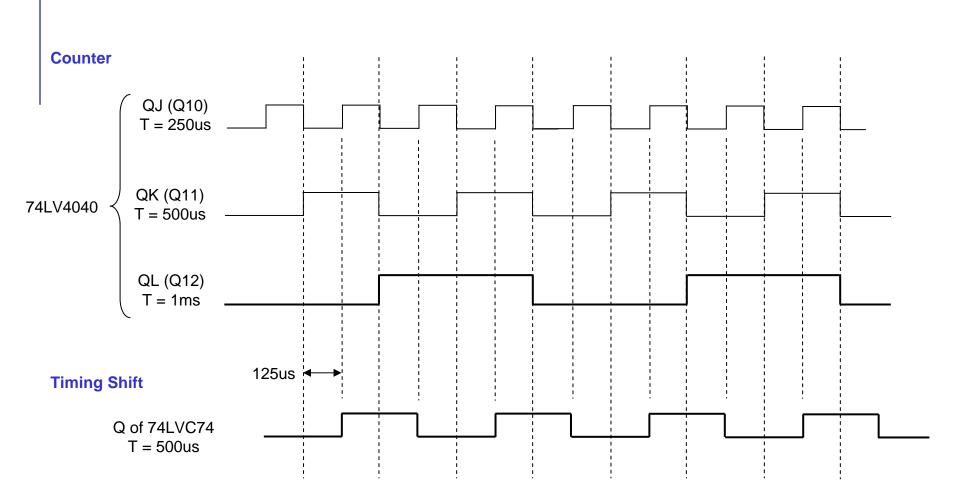

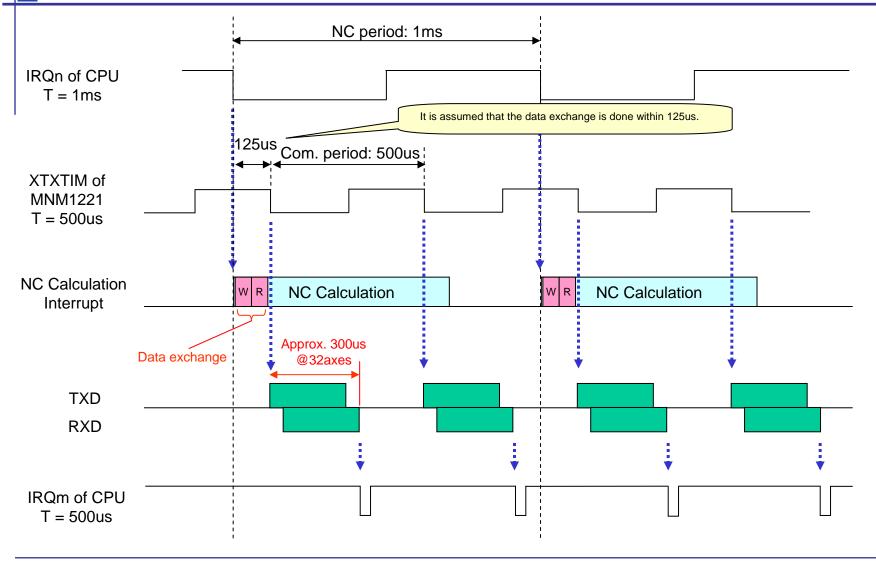

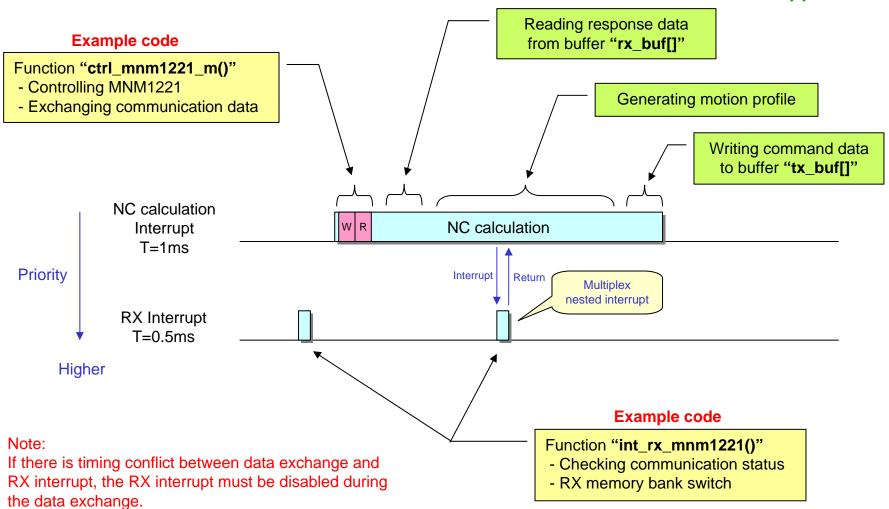

# Example for CPU without Internal Timer

# **Timing Circuit**

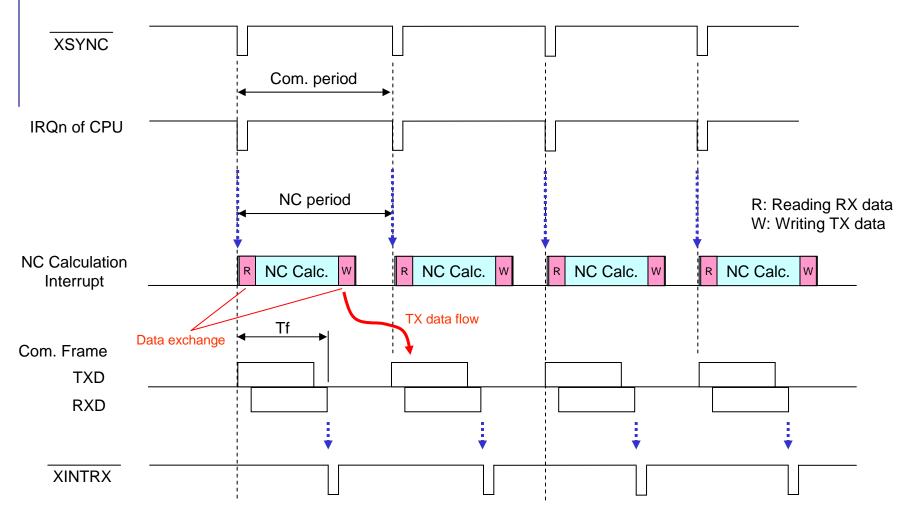

# **Timing Chart 1**

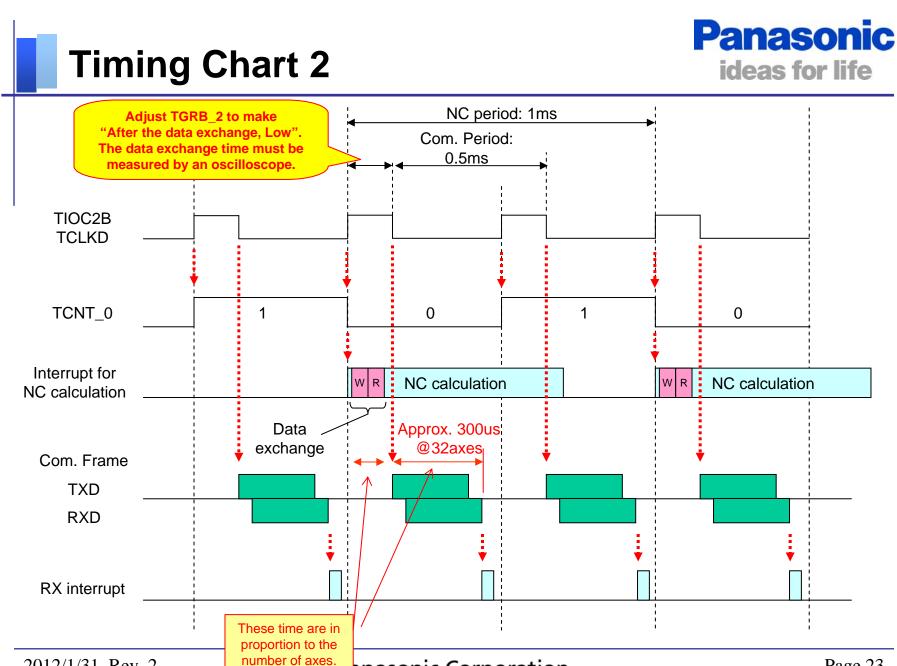

# **Timing Chart 2**

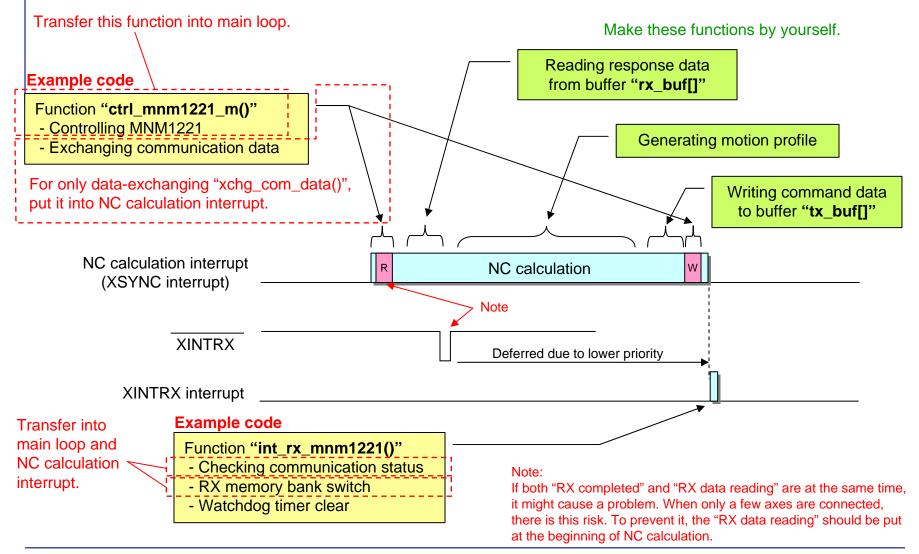

# Location of Example Codes

### **Location of Example Codes**

These functions have to be made by yourself.

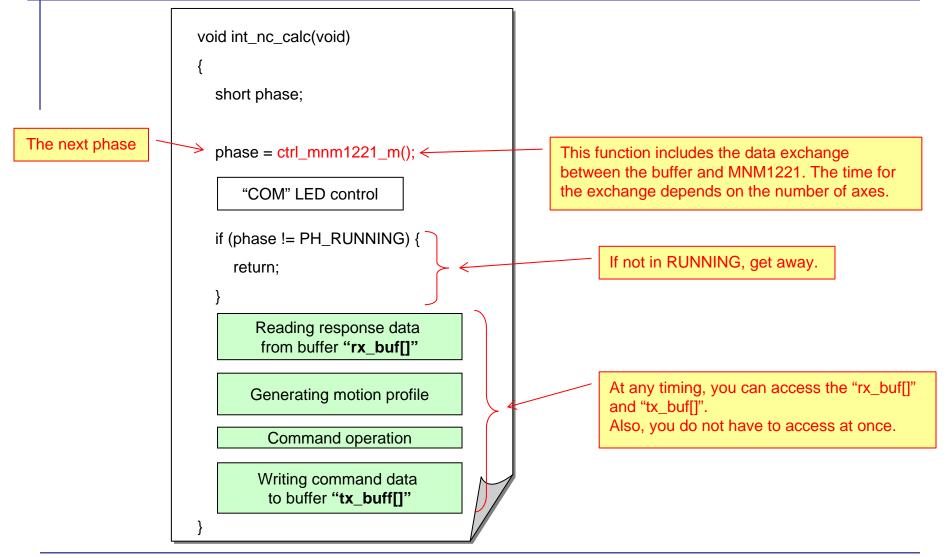

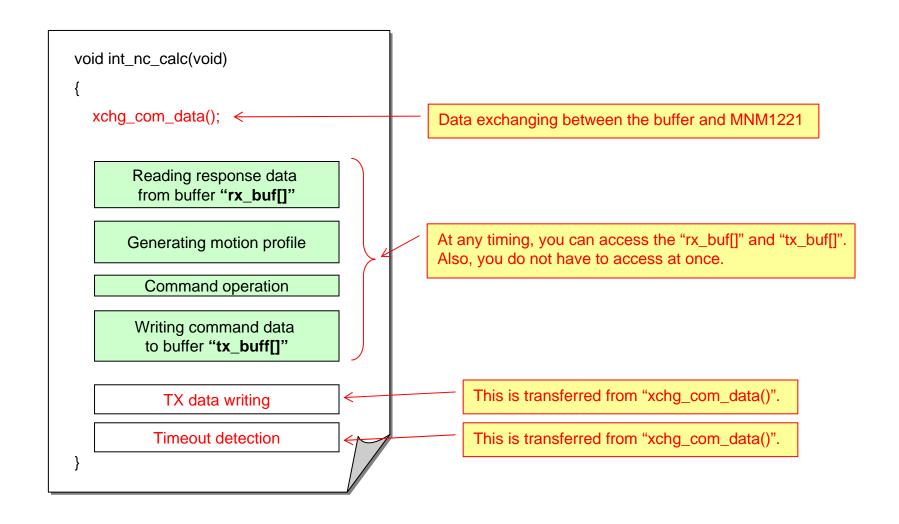

# An Example of NC Calculation

Panasonic

ideas for life

# Notes of Using Example Codes

### Data Structure (32bit)

The following shows the structure of one element of tx\_buf[] or rx\_buf[] array **when 32bit bus access**.

|                              |         | Bit   | Bit | Bit |       | Bit | Bit |       | Bit | Bit |       | Bit |

|------------------------------|---------|-------|-----|-----|-------|-----|-----|-------|-----|-----|-------|-----|

|                              |         | 31    | 24  | 23  |       | 16  | 15  |       | 8   | 7   |       | 0   |

|                              | data[0] | byte3 |     |     | byte2 |     |     | byte1 |     |     | byte0 |     |

| One element                  | data[1] | byte7 |     |     | byte6 |     |     | byte5 |     |     | byte4 |     |

| of tx_buf[] ≺<br>or rx_buf[] | data[2] | byteB |     |     | byteA |     |     | byte9 |     |     | byte8 |     |

|                              | data[3] | byteF |     |     | byteE |     |     | byteD |     |     | byteC |     |

"byte0 to F" is corresponding to contents of a data block consisting of 16bytes.

#### **Data Structure (16bit)**

The following shows the structure of one element of tx\_buf[] or rx\_buf[] array when 16bit bus access.

|                              |         | Bit<br>15 | Bit Bit 8 |       | Bit<br>0 |  |

|------------------------------|---------|-----------|-----------|-------|----------|--|

|                              | data[0] | byte1     |           | byte0 |          |  |

|                              | data[1] | byte3     |           | byte2 |          |  |

|                              | data[2] | byte5     |           | byte4 |          |  |

| One element                  | data[3] | byte7     |           | byte6 |          |  |

| of tx_buf[] {<br>or rx_buf[] | data[4] | byte9     |           | byte8 |          |  |

|                              | data[5] | byteB     |           | byteA |          |  |

|                              | data[6] | byteD     |           | byteC |          |  |

|                              | data[7] | byteF     |           | byteE |          |  |

"byte0 to F" is corresponding to contents of a data block consisting of 16bytes.

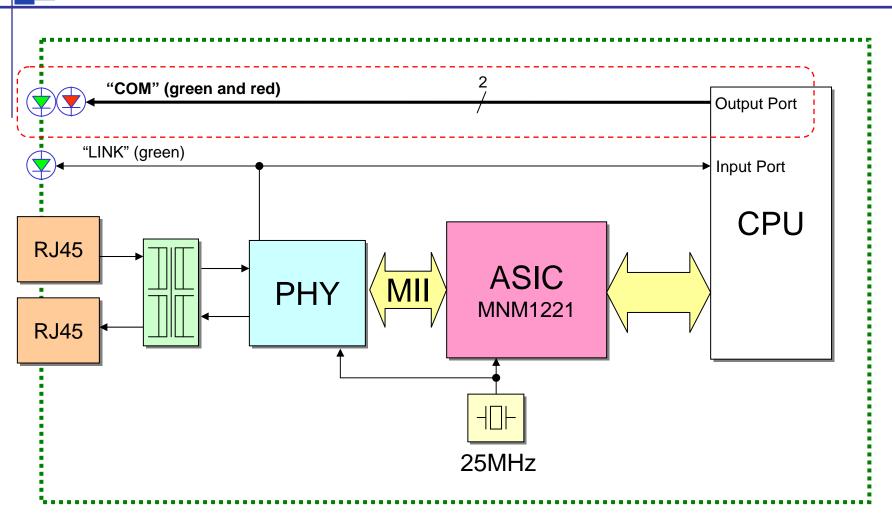

### **Status LEDs for Communication**

**Panasonic**

ideas for life

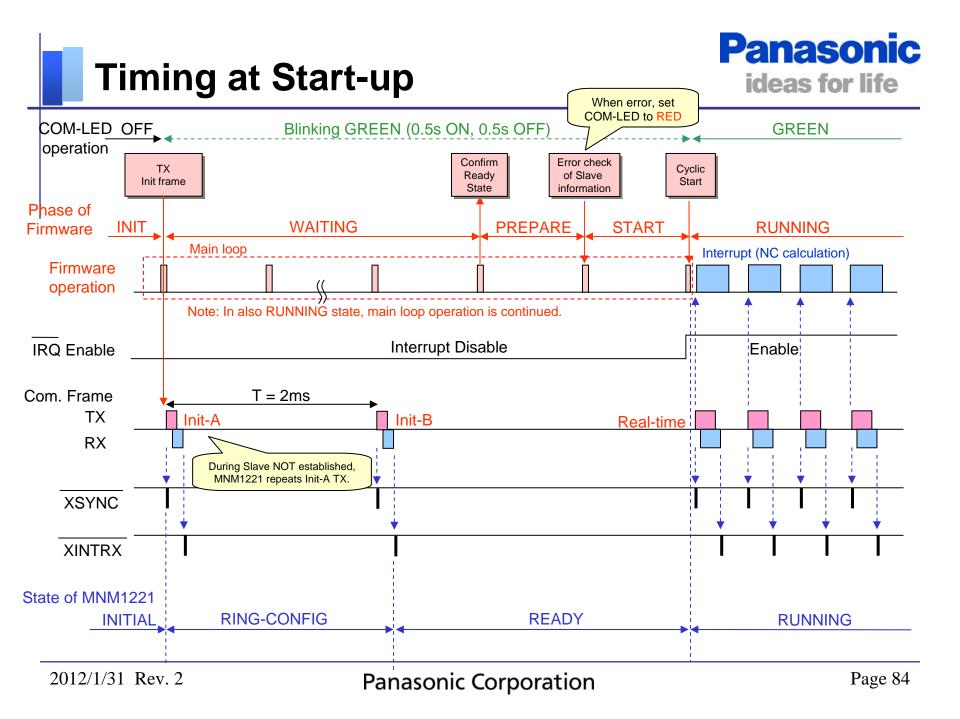

### "COM" LED Operation

"COM" LED which has red and green lights should be operated as follows:

| Normally | Return value of ctrl_mnm1221_m() | "COM" LED operation                   |  |  |

|----------|----------------------------------|---------------------------------------|--|--|

|          | PH_INIT                          | Disappearance                         |  |  |

|          | PH_WAITING                       |                                       |  |  |

|          | PH_PREPARE                       | Flashing Green<br>(0.5s ON, 0.5s OFF) |  |  |

|          | PH_START                         |                                       |  |  |

|          | PH_RUNNING                       | Solid Green                           |  |  |

| Error detected | Contents of error                                        | "COM" LED operation                 |

|----------------|----------------------------------------------------------|-------------------------------------|

|                | Timeout in RUNNING state                                 | Flashing Red<br>(0.5s ON, 0.5s OFF) |

|                | Mismatch of slave information<br>(e.g. duplicate MAC-ID) | Solid Red                           |

Notes:

- Solid Red means that a system reset is necessary to release the error.

- Either green or red must be lighted.

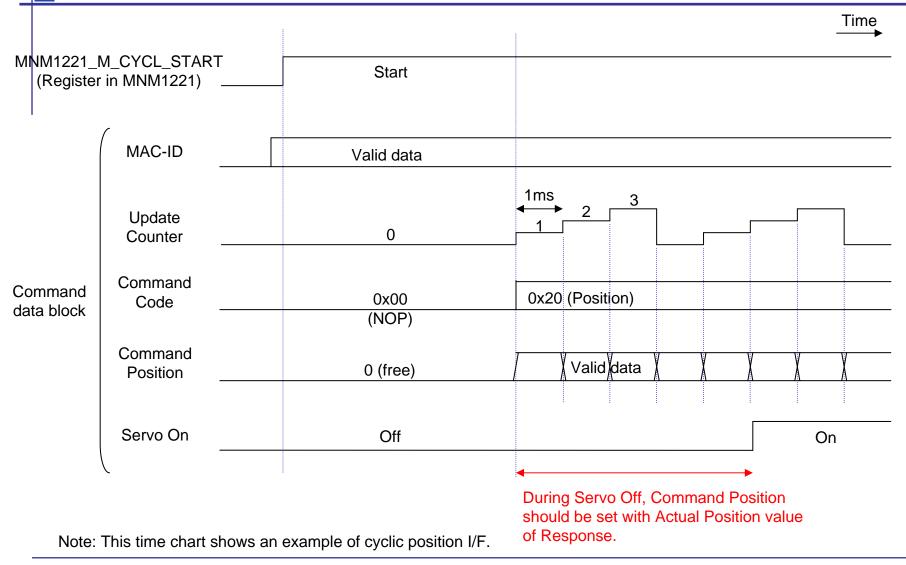

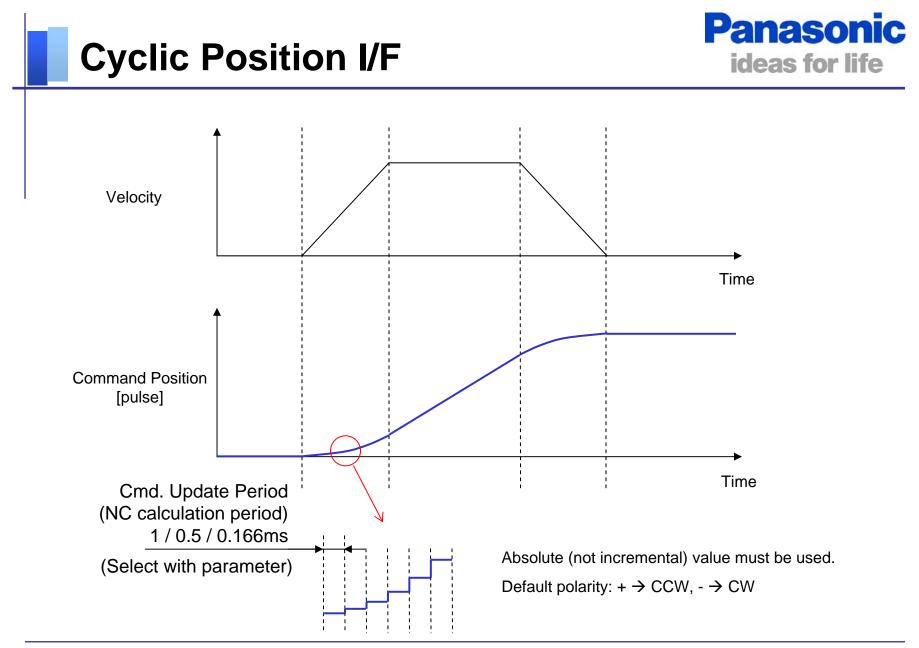

# Overview of Cyclic Position I/F

Data Block

|       | Command (TX)    |             |       |            |          |            |             |             |       | Response (RX) |                                                 |               |           |            |             |             |            |

|-------|-----------------|-------------|-------|------------|----------|------------|-------------|-------------|-------|---------------|-------------------------------------------------|---------------|-----------|------------|-------------|-------------|------------|

|       | bit7            | bit6        | bit5  | bit4       | bit3     | bit2       | bj          | bit0        |       | bit7          | bit6                                            | bit5          | bit4      | bit3       | bit2        | bit1        | bit0       |

| byte0 | 0<br>(CMD)      |             |       |            |          |            |             |             | byte0 | 1<br>(RSP)    |                                                 | Counter<br>ho |           | Ad         | ctual MAC-  | ·ID         |            |

| byte1 | 0               |             |       | Сог        | mmand Co | ode        |             |             | byte1 | CMD<br>Error  |                                                 |               | Com       | mand Code  | Echo        |             |            |

| byte2 | Servo<br>On     | 0           | 0     | Gain<br>SW | TL<br>SW | HM<br>Ctrl | 0           | 0           | byte2 | Servo<br>Act. | Servo<br>Ready                                  | Alarm         | Warn.     | TL         | HM<br>Comp. | In<br>Prog. | In<br>Pos. |

| byte3 | Hard<br>Stop    | SMT<br>Stop | Pause | 0          | SL<br>SW | 0          | EX-<br>OUT2 | EX-<br>OUT1 | byte3 | SI-<br>MO5    | SI-<br>MO4                                      | EXT<br>3      | EXT<br>2  | SI-<br>MO1 | Home        | РОТ         | NOT        |

| byte4 |                 |             |       |            |          |            | Low         | byte        | byte4 |               | Low byte                                        |               |           |            |             |             | oyte       |

| byte5 |                 |             |       | Command    | Position |            | Low Mid     | dle byte    | byte5 |               | Actual Position Low Middle by<br>High Middle by |               |           |            |             | lle byte    |            |

| byte6 |                 |             |       | oommana    |          |            | High Mid    | ldle byte   | byte6 |               |                                                 |               |           |            |             | dle byte    |            |

| byte7 |                 |             |       |            |          |            | High        | byte        | byte7 |               | High byte                                       |               |           |            | oyte        |             |            |

| byte8 |                 |             |       |            |          |            | Low         | byte        | byte8 |               | Low byte                                        |               |           |            | oyte        |             |            |

| byte9 |                 |             |       | Comman     | d Data 2 |            | Low Mid     | dle byte    | byte9 |               | Response Data 2 Low Middle                      |               |           |            |             | ile byte    |            |

| byteA |                 |             |       | Comman     | a Data 2 |            | High Mid    | ldle byte   | byteA | High Middle b |                                                 |               |           |            | dle byte    |             |            |

| byteB |                 |             |       |            |          |            | High        | byte        | byteB |               |                                                 |               |           |            |             | High l      | oyte       |

| byteC |                 | Low byte    |       |            |          |            |             |             | byteC |               |                                                 |               |           |            |             | Low b       | ovte       |

| byteD | Low Middle byte |             |       |            |          |            |             | byteD       |       |               |                                                 | Dognor        | se Data 3 |            | Low Mide    | •           |            |

| byteE |                 |             |       | Comman     | u Data 3 |            | High Mid    | ldle byte   | byteE |               |                                                 |               | Respons   | se Data 5  |             | High Mid    | dle byte   |

| byteF |                 |             |       |            |          |            | High        | byte        | byteF |               |                                                 |               |           |            |             | High l      | byte       |

Note: In cyclic position I/F, at least red portions must be supported.

#### **Command at Start-up**

# Overview of Profile Position I/F

### Command

|        | Bit7         | Bit6           | Bit5                            | Bit4       | Bit3      | Bit2           | Bit1        | Bit0        |  |  |  |

|--------|--------------|----------------|---------------------------------|------------|-----------|----------------|-------------|-------------|--|--|--|

| Byte0  | C/R<br>(0)   | Update         | Update Counter MAC-ID (0 to 31) |            |           |                |             |             |  |  |  |

| Byte1  | TMG<br>CNT   |                |                                 | 17h (      | Command ( | Code)          |             |             |  |  |  |

| Byte2  | Servo<br>On  | 0              | 0                               | Gain<br>SW | TL SW     | Homing<br>Ctrl | 0           | 0           |  |  |  |

| Byte3  | Hard<br>Stop | Smooth<br>Stop | Pause                           | 0          | SL SW     | 0              | EX-<br>OUT2 | EX-<br>OUT1 |  |  |  |

| Byte4  |              |                |                                 |            |           |                |             |             |  |  |  |

| Byte5  |              |                |                                 | Target     | Position  |                |             |             |  |  |  |

| Byte6  |              |                |                                 | Targer     | Position  |                |             |             |  |  |  |

| Byte7  |              |                |                                 |            |           |                |             |             |  |  |  |

| Byte8  |              |                |                                 | Туре       | Code 🤜    | M              | ode,        |             |  |  |  |

| Byte9  |              |                |                                 | (          | )         |                | /Abs        |             |  |  |  |

| Byte10 |              |                |                                 | (          | )         |                |             |             |  |  |  |

| Byte11 |              |                |                                 | Monit      | or Sel    |                |             |             |  |  |  |

| Byte12 |              |                |                                 |            |           |                |             |             |  |  |  |

| Byte13 |              |                |                                 | Torest     | Speed     |                |             |             |  |  |  |

| Byte14 |              |                |                                 | rarget     | Speed     |                |             |             |  |  |  |

| Byte15 |              |                |                                 |            |           |                |             |             |  |  |  |

|        | Bit7               | Bit6               | Bit5                                           | Bit4             | Bit3              | Bit2               | Bit1           | Bit0           |  |  |  |  |  |  |

|--------|--------------------|--------------------|------------------------------------------------|------------------|-------------------|--------------------|----------------|----------------|--|--|--|--|--|--|

| Byte0  | C/R<br>(1)         |                    | Update Counter<br>Echo Actual MAC-ID (0 to 31) |                  |                   |                    |                |                |  |  |  |  |  |  |

| Byte1  | CMD<br>Error       |                    | 17h (Command Code Echo)                        |                  |                   |                    |                |                |  |  |  |  |  |  |

| Byte2  | Servo<br>Active    | Servo<br>Ready     | Alarm                                          | Warning          | Torque<br>Limited | Homing<br>Complete | In<br>Progress | In<br>Position |  |  |  |  |  |  |

| Byte3  | SI-MON5<br>/E-STOP | SI-MON4<br>/EX-SON | SI-MON3<br>/EXT3                               | SI-MON2<br>/EXT2 | SI-MON1<br>/EXT1  | Home               | POT<br>/NOT    | NOT<br>/POT    |  |  |  |  |  |  |

| Byte4  |                    |                    |                                                |                  |                   |                    |                |                |  |  |  |  |  |  |

| Byte5  |                    | Actual Position    |                                                |                  |                   |                    |                |                |  |  |  |  |  |  |

| Byte6  |                    |                    |                                                | Actual           | -05111011         |                    |                |                |  |  |  |  |  |  |

| Byte7  |                    |                    |                                                |                  |                   |                    |                |                |  |  |  |  |  |  |

| Byte8  |                    |                    |                                                | Туре Со          | de Echo           |                    |                |                |  |  |  |  |  |  |

| Byte9  | ERR                | WNG                | 0                                              | BUSY             | PSL<br>/NSL       | NSL<br>/PSL        | NEAR           | Latch<br>Compl |  |  |  |  |  |  |

| Byte10 |                    |                    |                                                | (                | )                 |                    |                |                |  |  |  |  |  |  |

| Byte11 |                    |                    |                                                | Monitor          | Sel Echo          |                    |                |                |  |  |  |  |  |  |

| Byte12 |                    |                    |                                                |                  |                   |                    |                |                |  |  |  |  |  |  |

| Byte13 | 1                  |                    |                                                | Monite           |                   |                    |                |                |  |  |  |  |  |  |

| Byte14 |                    |                    |                                                | wonito           | or Data           |                    |                |                |  |  |  |  |  |  |

| Byte15 |                    |                    |                                                |                  |                   |                    |                |                |  |  |  |  |  |  |

Start

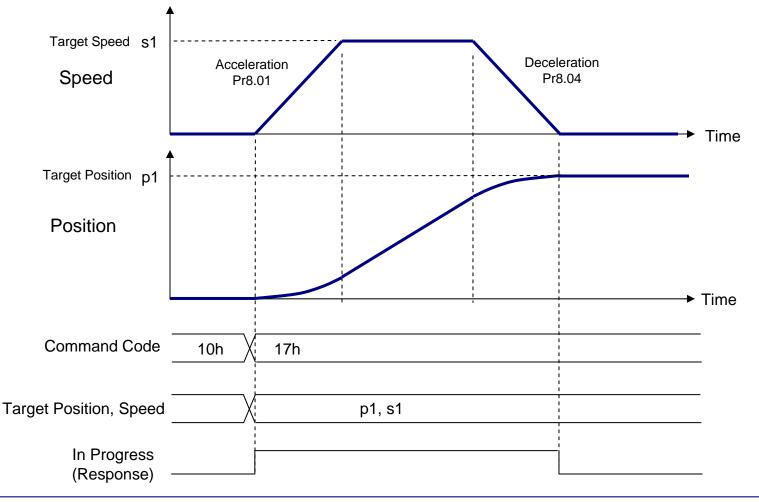

When "In Progress" = 0, a change of Command Code 10h to 17h makes servo start motion. Acceleration and deceleration are preset with parameter. Abs/Inc is set with Type Code at start.

2012/1/31 Rev. 2

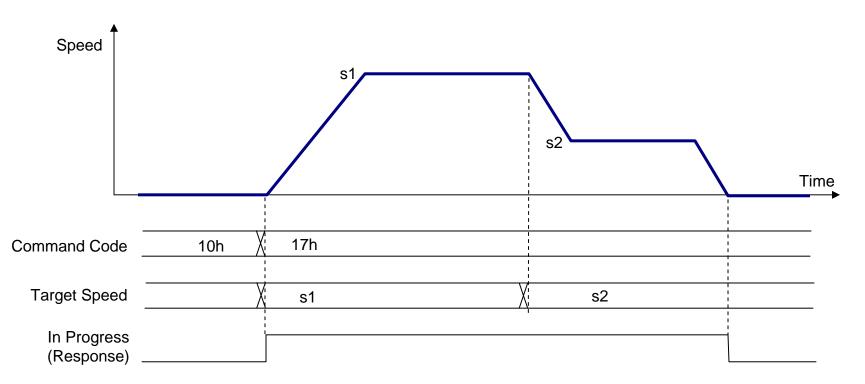

### **Changing T Speed in Motion**

When "In Progress" = 1, target speed can be changed. Even if changing target speed to 0 or Pause to 1, "In Progress" keeps 1 during stop.

# Modifying the Example Code

### **Definition for Bus Access**

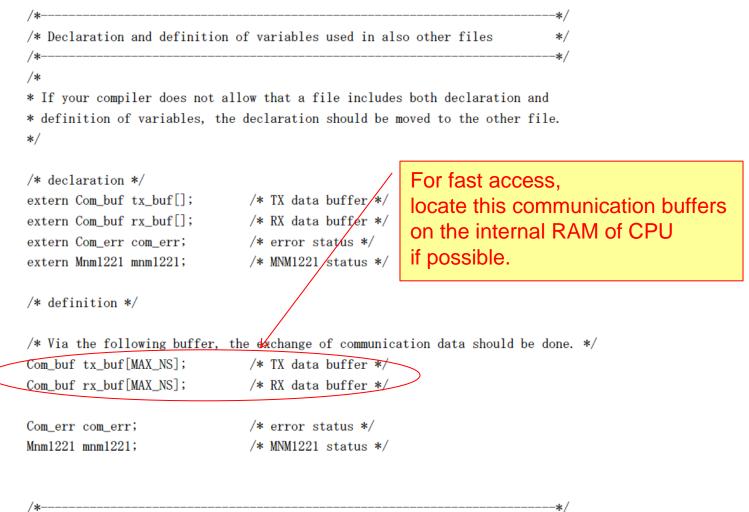

### **Definition of Variables**

#### mnm1221\_m.c

Panasonic Corporation

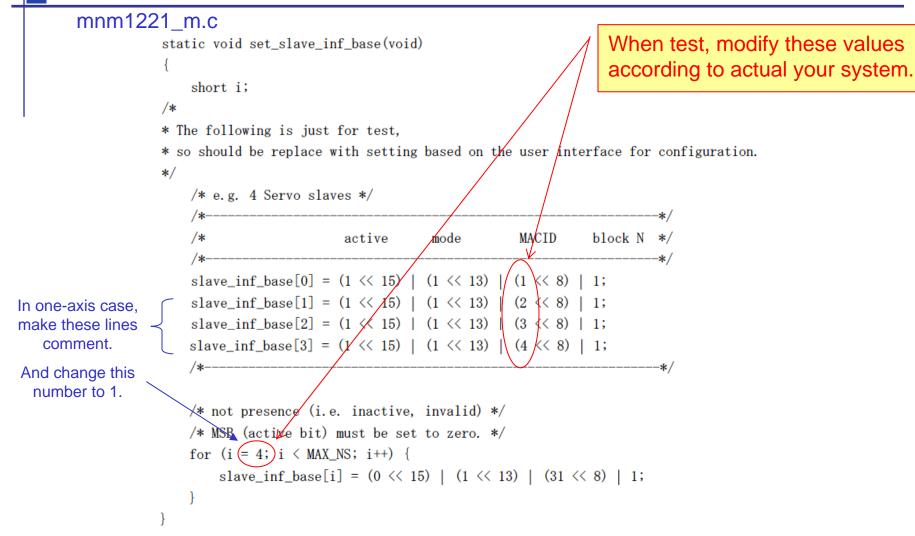

# **Slave Information Table**

# **Slave Information Table (Cont.)**

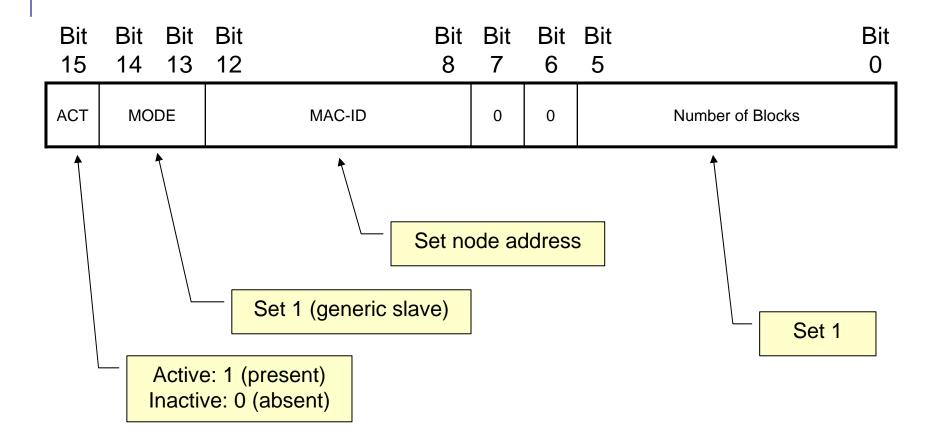

Structure of Slave Information data:

Panasonic

ideas for life

# **Style of Initializing Variables**

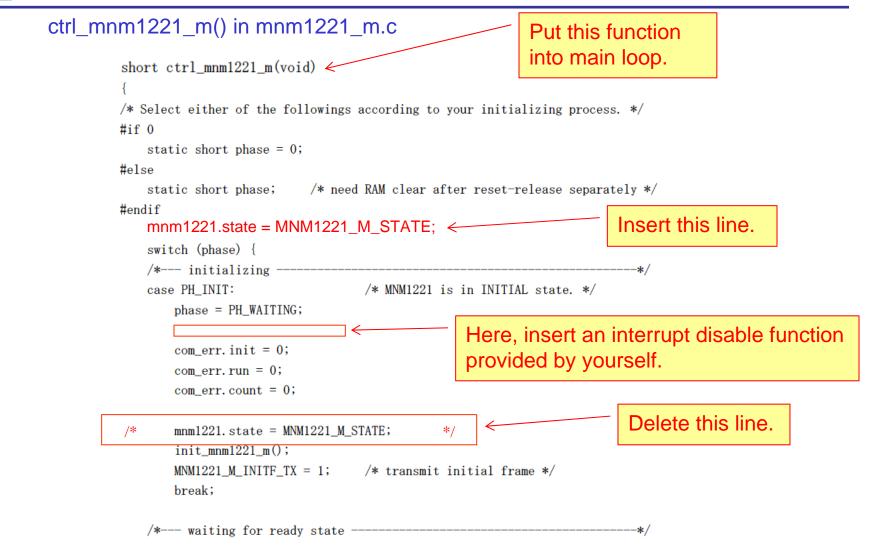

ctrl\_mnm1221\_m() in mnm1221\_m.c

To set variable "phase" to 0 after reset, select this value (0 or 1) according to your initializing process.

/\* Select either of the followings according to your initializing process. \*/

#if 0

```

static short phase = 0;

```

#else

```

static short phase; /* need RAM clear after reset-release separately */

#endif

```

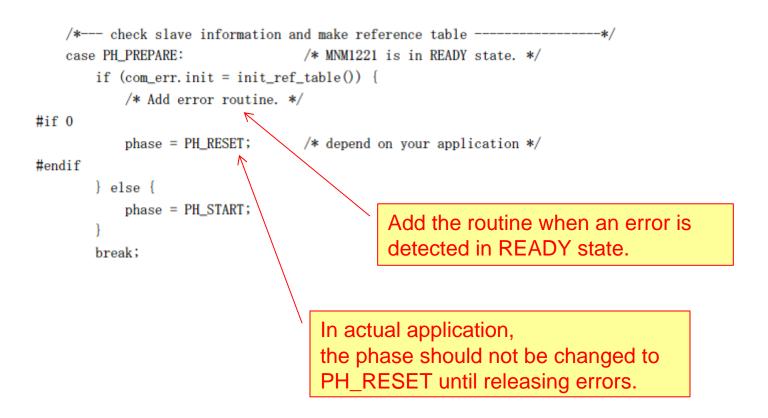

### **Checking Slave Information**

#### ctrl\_mnm1221\_m() in mnm1221\_m.c

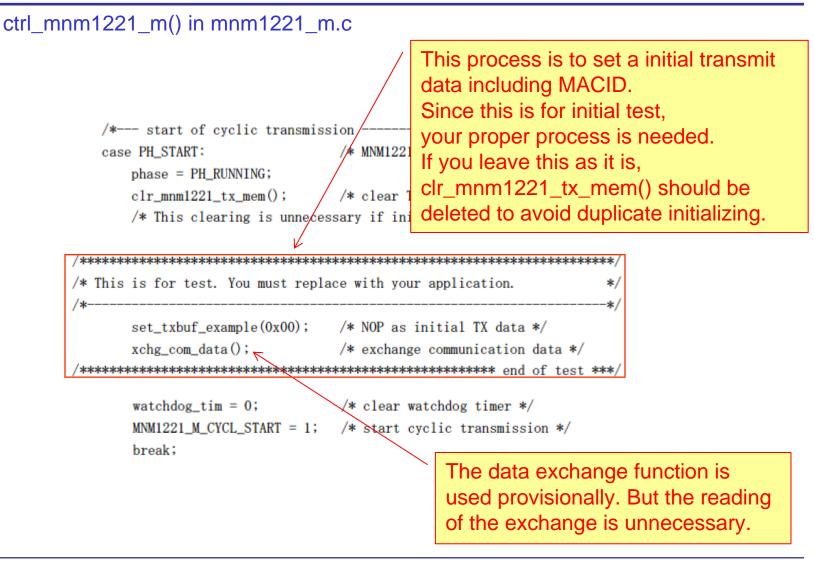

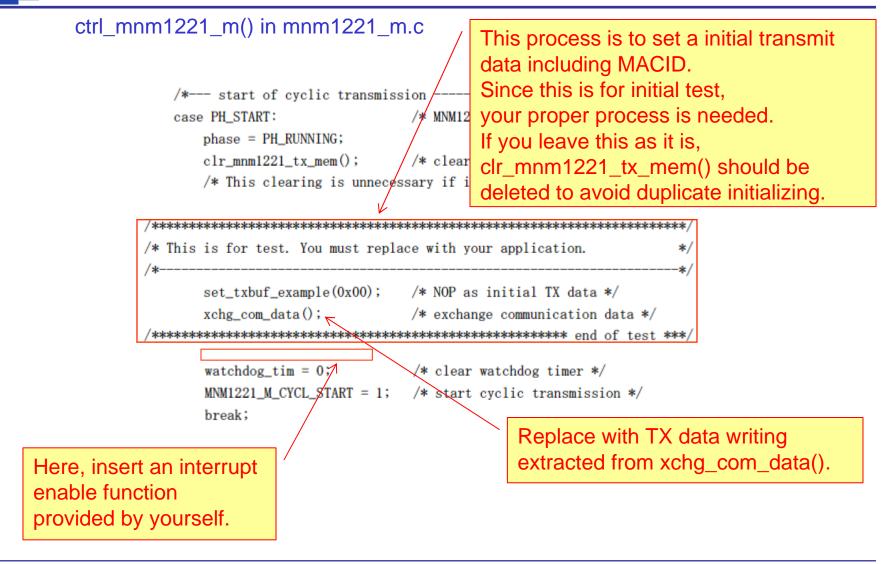

# **Starting Cyclic Transmission**

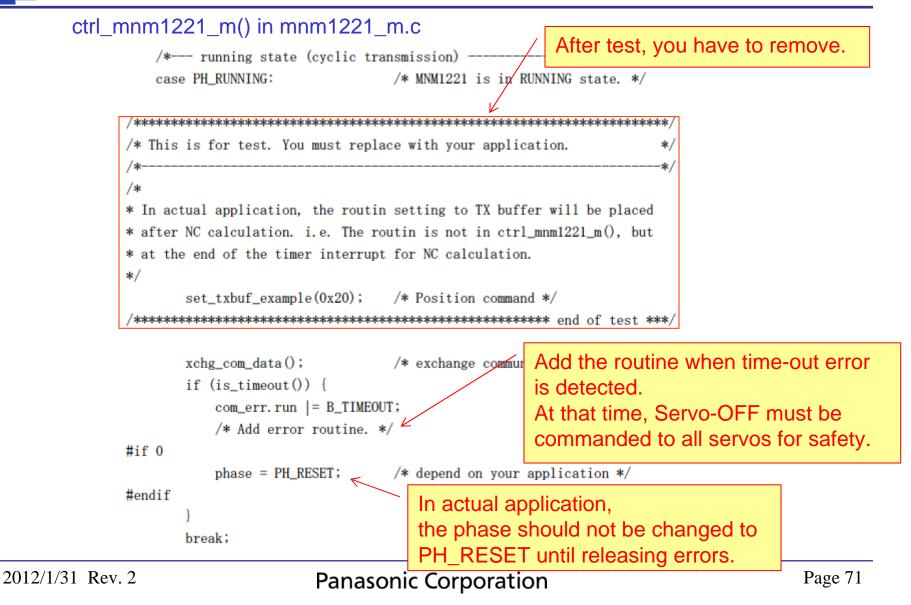

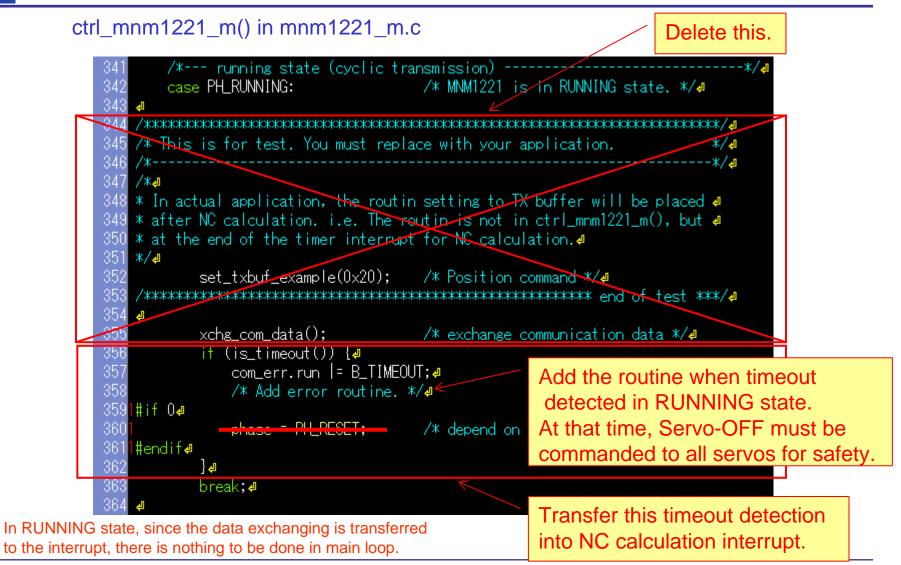

### In Running State

# Chapter 2 Internal-Timer Using System

## The Point of System

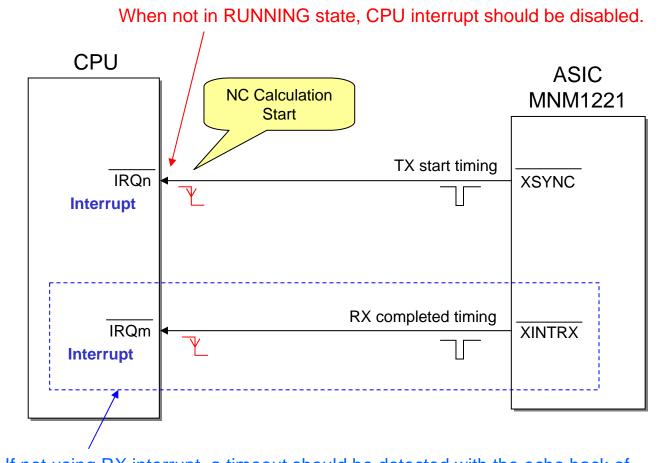

- Set both "Command Update Period" and "Communication Period" to the same time.

- Start NC calculation interrupt with MNM1221 XSYNC.

- If not using RX interrupt, detect timeout error by software using "Update Counter Echo".

# **Period Setting of A5N Drive**

Set both command update period and communication period to the same. Default setting must be changed.

|     | Update  | Com.    | Setting |        |  |  |

|-----|---------|---------|---------|--------|--|--|

| ' I | Period  | Period  | Pr7.20  | Pr7.21 |  |  |

| -   | 1.000ms | 1.000ms | 6       | 1      |  |  |

|     | 1.000ms | 0.500ms | 3       | 2      |  |  |

| -   | 0.500ms | 0.500ms | 3       | 1      |  |  |

| →   | 0.166ms | 0.166ms | 1       | 1      |  |  |

|     | 0.166ms | 0.083ms | 0       | 2      |  |  |

|        | Name                                     | Range | Description                                                                      |  |  |

|--------|------------------------------------------|-------|----------------------------------------------------------------------------------|--|--|

| Pr7.20 | Communication Period 0 to                |       | 0: 0.083ms<br>1: 0.166ms<br>3: 0.5ms<br>6: 1.0ms<br>Else: Do not set. (Reserved) |  |  |

| Pr7.21 | Ratio of<br>Command Update Period 1 to 2 |       | Command Update / Communication Period<br>1: 1<br>2: 2 (Com.=0.5ms case only)     |  |  |

2012/1/31 Rev. 2

# **Goal of Timing Control**

\* One frame contains data of all slave nodes, and its length depends on the number of connected nodes.

# Example for an Embedded CPU

# **Timing Circuit**

If not using RX interrupt, a timeout should be detected with the echo back of Update Counter in the data block.

### **Recommended Timing**

Tf: approx. 11us@1-axis to 300us@32-axis

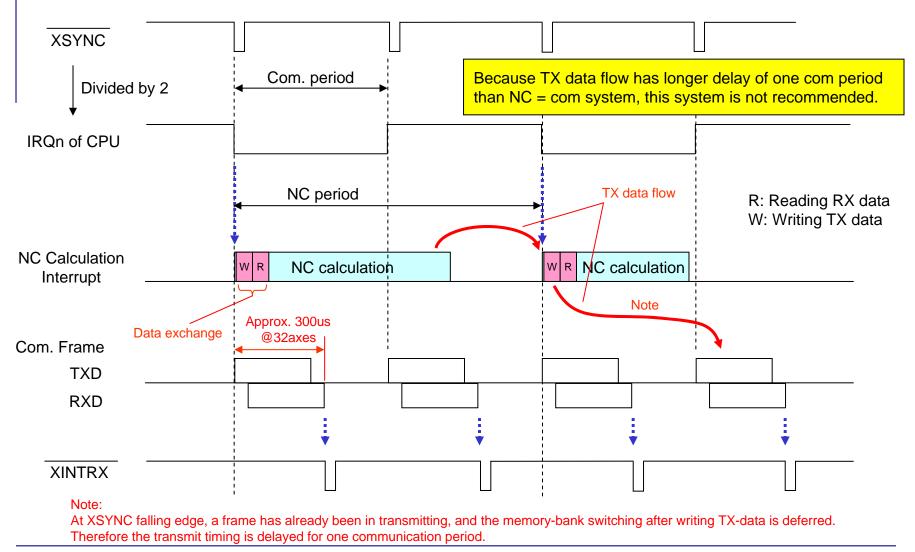

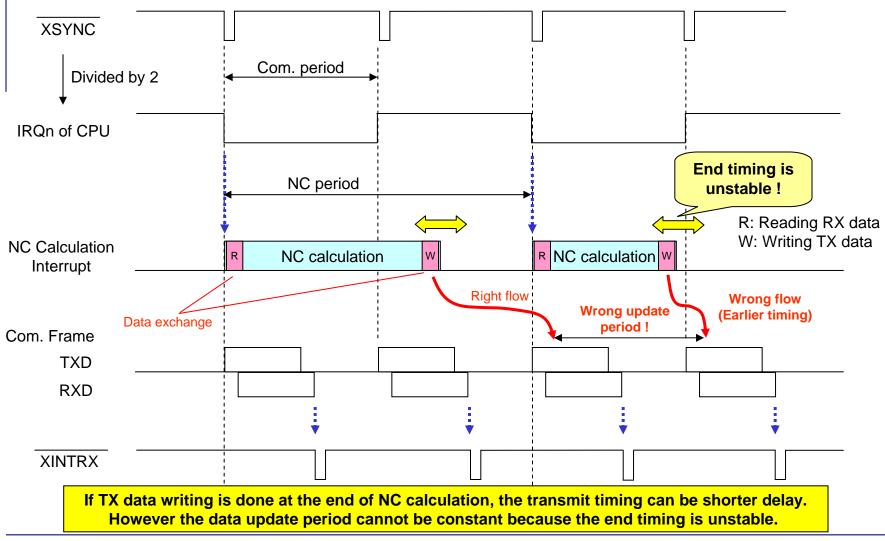

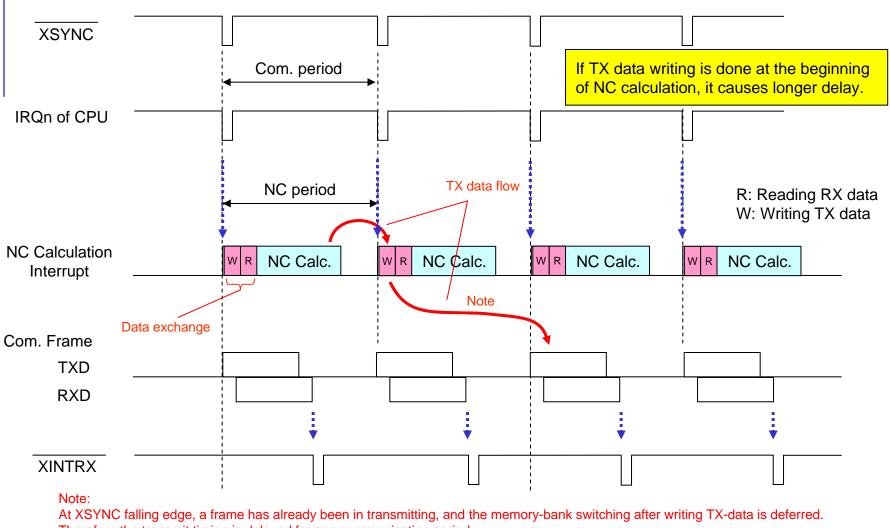

# **NOT Recommended Timing**

Therefore the transmit timing is delayed for one communication period.

Panasonic Corporation

**Panasonic**

ideas for life

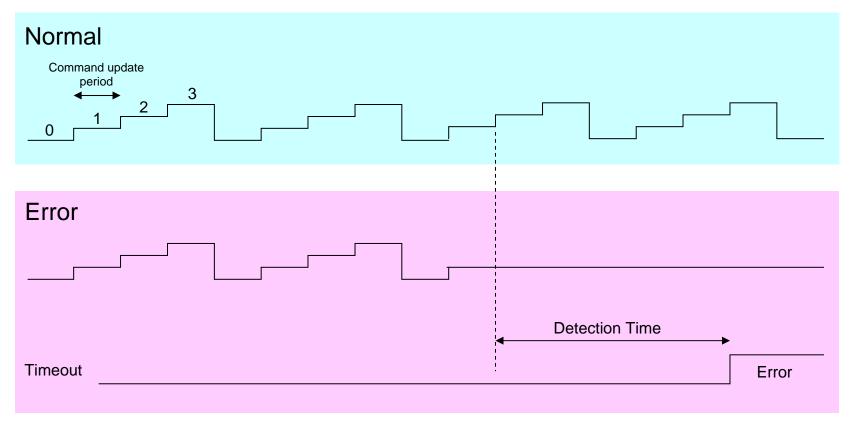

# Timeout Detection Example for Not Using RX Interrupt

# **Update Counter**

|       | Command (TX)                       |                                  |       |            |          |            |             |             |  |

|-------|------------------------------------|----------------------------------|-------|------------|----------|------------|-------------|-------------|--|

|       | bit7                               | bin                              | bit5  | bit4       | bit3     | bit2       | bit1        | bit0        |  |

| byte0 | 0<br>(CMD)                         | Update Counter MAC-ID            |       |            |          |            |             |             |  |

| byte1 | 0                                  |                                  |       | Со         | mmand Co | ode        |             |             |  |

| byte2 | Servo<br>On                        | 0                                | 0     | Gain<br>SW | TL<br>SW | HM<br>Ctrl | 0           | 0           |  |

| byte3 | Hard<br>Stop                       | SMT<br>Stop                      | Pause | 0          | SL<br>SW | 0          | EX-<br>OUT2 | EX-<br>OUT1 |  |

| byte4 |                                    | Low byte                         |       |            |          |            |             |             |  |

| byte5 |                                    | Command Position Low Middle byte |       |            |          |            |             |             |  |

| byte6 |                                    | High Middle byte<br>High byte    |       |            |          |            |             | dle byte    |  |

| byte7 |                                    |                                  |       |            |          |            |             | byte        |  |

| byte8 |                                    | Low byte                         |       |            |          |            |             |             |  |

| byte9 | Low Middle byte                    |                                  |       |            |          |            |             |             |  |

| byteA |                                    | Command Data 2 High Middle byte  |       |            |          |            |             |             |  |

| byteB |                                    | High byte                        |       |            |          |            |             |             |  |

| byteC | Low byte                           |                                  |       |            |          |            |             |             |  |

| byteD | Command Data 3<br>High Middle byte |                                  |       |            |          |            |             | dle byte    |  |

| byteE |                                    |                                  |       |            |          |            |             | dle byte    |  |

| byteF |                                    | High byte                        |       |            |          |            |             |             |  |

#### Response (RX)

|       | bit7            | b. 6                             | bit5              | bit4          | bit3       | bit2        | bit1        | bit0       |  |

|-------|-----------------|----------------------------------|-------------------|---------------|------------|-------------|-------------|------------|--|

| byte0 | 1<br>(RSP)      | -                                | Counter<br>cho    | Actual MAC-ID |            |             |             |            |  |

| byte1 | CMD<br>Error    |                                  | Command Code Echo |               |            |             |             |            |  |

| byte2 | Servo<br>Act.   | Servo<br>Ready                   | Alarm             | Warn.         | TL         | HM<br>Comp. | In<br>Prog. | In<br>Pos. |  |

| byte3 | SI-<br>MO5      | SI-<br>MO4                       | EXT<br>3          | EXT<br>2      | SI-<br>MO1 | Home        | РОТ         | NOT        |  |

| byte4 |                 |                                  |                   |               |            |             | Low b       | vte        |  |

| byte5 | Low Middle byte |                                  |                   |               |            |             |             |            |  |

| byte6 |                 | Actual Position High Middle byte |                   |               |            |             |             |            |  |

| byte7 |                 | High byte                        |                   |               |            |             |             | yte        |  |

| byte8 |                 | Low byte                         |                   |               |            |             |             |            |  |

| byte9 | Low Middle byte |                                  |                   |               |            |             |             | -          |  |

| byteA |                 | Response Data 2 High Middle byte |                   |               |            |             |             |            |  |

| byteB |                 | High byte                        |                   |               |            |             |             |            |  |

| byteC | Low byte        |                                  |                   |               |            |             |             |            |  |

| byteD | Low Middle byte |                                  |                   |               |            |             |             | -          |  |

| byteE |                 | Response Data 3 High Middle byte |                   |               |            |             |             | lle byte   |  |

| byteF |                 |                                  |                   | High byte     |            |             |             |            |  |

### **Timeout Detection**

If "Update Counter Echo" is not changed continuously for a certain time, timeout should be considered.

If timeout is detected, servo-off must be commanded to all axes for safety.

# Modifying the Example Code

See also corresponding clause in chapter 1. There are some abbreviations to prevent duplicate descriptions.

| Task                | Trigger      | Priority               | Period           | Operation                                                                                           |

|---------------------|--------------|------------------------|------------------|-----------------------------------------------------------------------------------------------------|

| Main loop           | -            | -                      | -                | <ul> <li>Controlling MNM1221<br/>(including com-status check)</li> <li>"COM" LED control</li> </ul> |

| XSYNC<br>Interrupt  | TX start     | -                      | e.g.<br>0.5ms    | <ul> <li>Communication data exchange</li> <li>NC calculation</li> <li>Timeout detection</li> </ul>  |

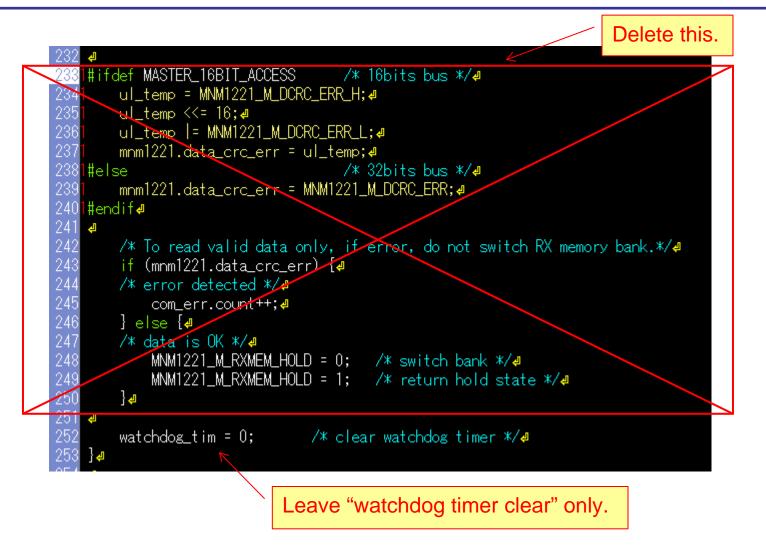

| XINTRX<br>Interrupt | RX completed | Lower<br>than<br>XSYNC | Same as<br>XSYNC | - Watchdog timer clear                                                                              |

Notes:

- The interrupts must be disabled until RUNNING state.

- If not using XINTRX interrupt, a timeout detection with Update Counter Echo is necessary.

## **Location of Example Codes**

## **An Example of Location**

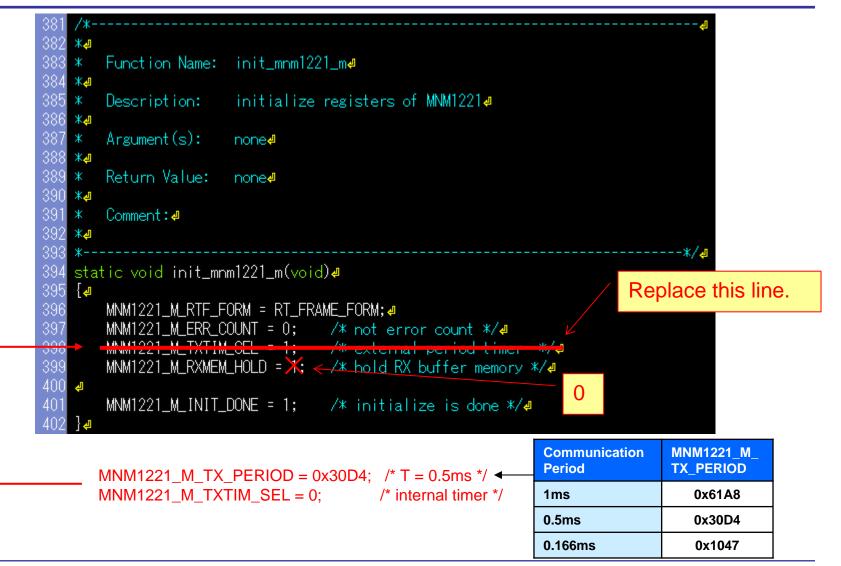

# **MNM1221** initializing

Panasonic

ideas for life

### **Reading State**

# **Starting Cyclic Transmission**

#### Panasonic ideas for life

# In Running State

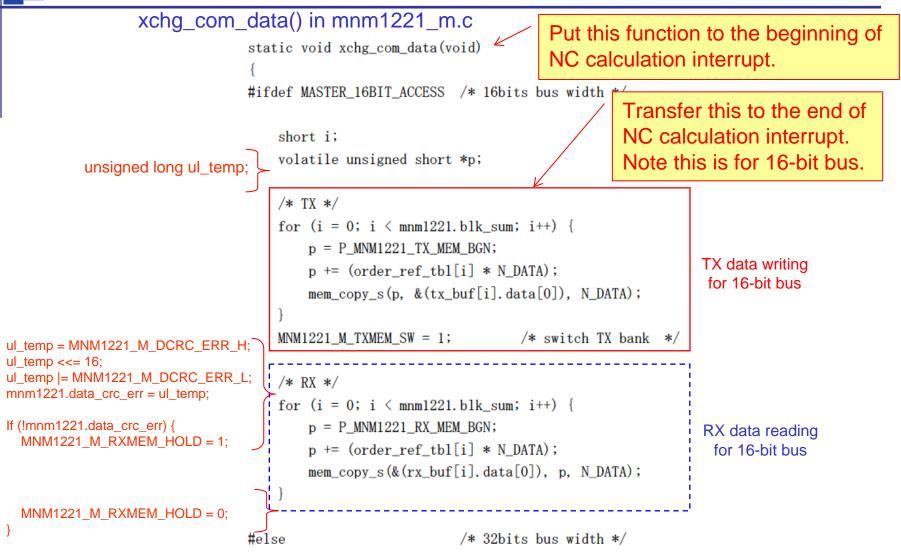

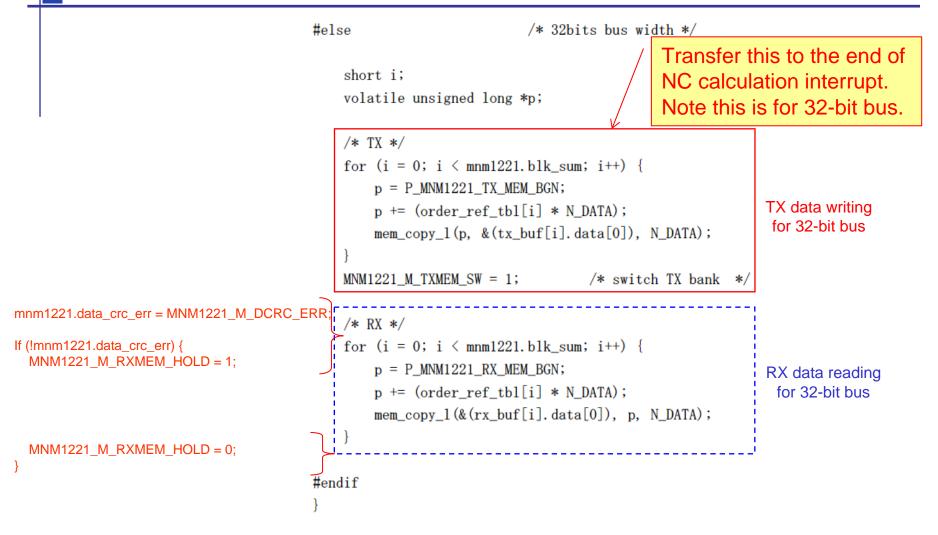

## **Data Exchanging**

2012/1/31 Rev. 2

# Data Exchanging (Cont.)

#### Panasonic ideas for life

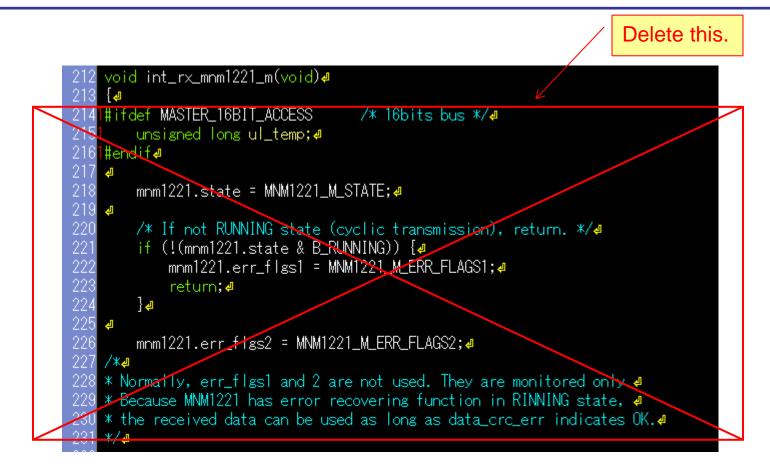

### **XINTRX Interrupt**

# **XINTRX Interrupt (Cont.)**

#### Panasonic ideas for life

### Appendix

### System Consideration for 2 times communication one NC calculation

This system is not recommended because of longer delay in TX data flow.

# **Timing Chart**